32. Безвентильные счетчики (асинхронные счетчики по произвольному модулю).

Относятся к асинхронным счетчикам. любой коэффициент счета можно представить в виде  , или

, или  , или

, или  .

.

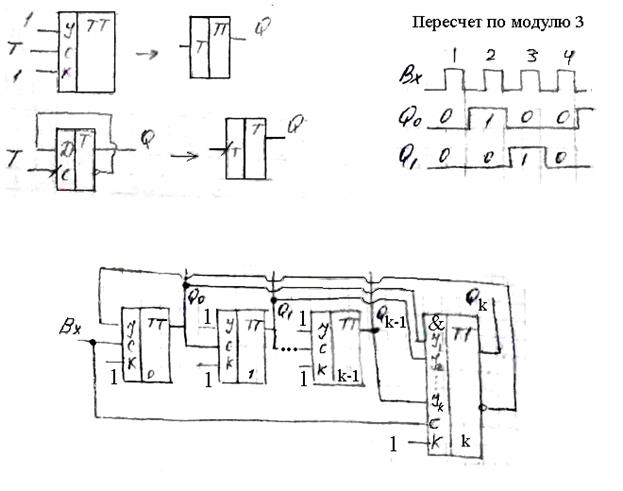

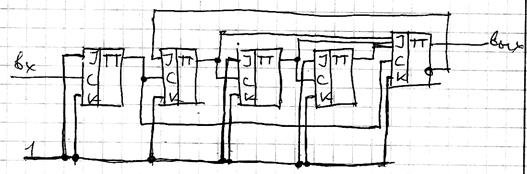

Сформулируем методику построения счетчика по модулю  . Для этого необходимо иметь K-разрядный двоичный счетчик и единичный JK-триггер, который должен иметь K входов J объединенных между собой конъюнктивно. Входной сигнал счетчика подается на вход K разрядного двоичного счетчика и на вход C единичного JK-триггера. Выходы Q K разрядного счетчика подаются соответственно на входы J единичного JK счетчика. На вход K единичного JK-триггера подается логическая «1». Выход

. Для этого необходимо иметь K-разрядный двоичный счетчик и единичный JK-триггер, который должен иметь K входов J объединенных между собой конъюнктивно. Входной сигнал счетчика подается на вход K разрядного двоичного счетчика и на вход C единичного JK-триггера. Выходы Q K разрядного счетчика подаются соответственно на входы J единичного JK счетчика. На вход K единичного JK-триггера подается логическая «1». Выход  единичного JK-триггера соединяется со входом J первого разряда двоичного счетчика. На вход K этого первого разряда счетчика подается «1». Выходом на пересчетные схемы является выход Q единичного JK-триггера. Состояние счетчика определяется выходным сигналом двоичного JK-триггера.

единичного JK-триггера соединяется со входом J первого разряда двоичного счетчика. На вход K этого первого разряда счетчика подается «1». Выходом на пересчетные схемы является выход Q единичного JK-триггера. Состояние счетчика определяется выходным сигналом двоичного JK-триггера.

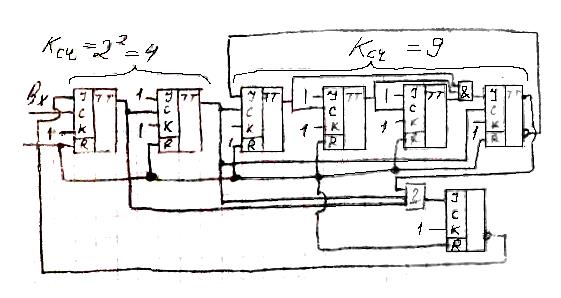

Название безвентильный условно, так как ЛЭ «&» нужен для объединения входов J1, …, Jk. При последовательном включении счетчиков модуль счета равен произведению MСЧ1*MСЧ2.

M =  . Каждый коэффициент реализуется самостоятельно

. Каждый коэффициент реализуется самостоятельно  ,

,  . Для увеличения произведения таких коэффициентов на 1 схема дополняется единичным JK-триггером. Сами группы счетчиков включаются последовательно, а единичный JK-триггер должен иметь столько J-входов, сколько имеется групп. При этом каждый триггер P-разрядного двоичного счетчика рассматривается как отдельная группа. Входной сигнал подается на вход счетчика первой группы, а также на вход C единичного JK-триггера. Его инверсный выход соединяется со входом J первого триггера. На вход K подается «1».

. Для увеличения произведения таких коэффициентов на 1 схема дополняется единичным JK-триггером. Сами группы счетчиков включаются последовательно, а единичный JK-триггер должен иметь столько J-входов, сколько имеется групп. При этом каждый триггер P-разрядного двоичного счетчика рассматривается как отдельная группа. Входной сигнал подается на вход счетчика первой группы, а также на вход C единичного JK-триггера. Его инверсный выход соединяется со входом J первого триггера. На вход K подается «1».

Kсч = 37 = 22(23+1)+1

Kсч = 18 = 2(23+1)

Недостатки:

1) схема асинхронна, следовательно понижено быстродействие

2) неестественный порядок изменения состояний (ест. 2K+1)

3) избыточное количество триггеров

4) требуются ЛЭ с числом входов, большим 1

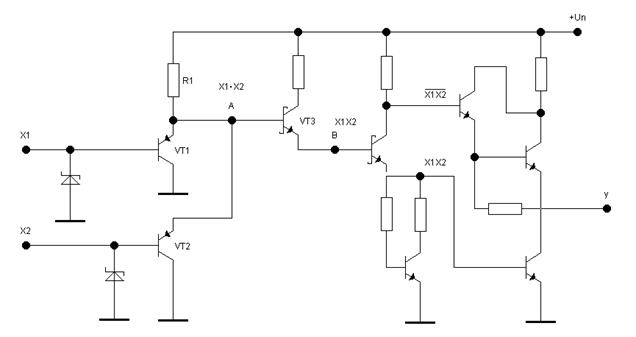

33. Базовый ЛЭ ТТЛШ (серия 1531)

КР1531ЛА3 – функция И-НЕ.

VT1, VT2, R1 – логическая схема И, выполнена на транзисторах типа p-n-p, включенных по схеме эмиттерного повторителя.

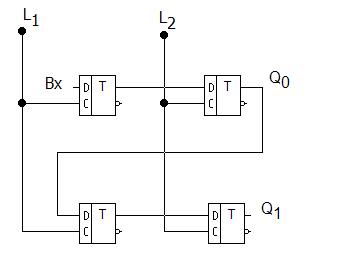

34. Двухтактные регистры сдвига

Используются одноступенчатые статические триггеры.

Применение триггеров:

1) Одноступенчатые статические - в регистрах памяти, в регистрах сдвига, только если используется 2-х фазная система синхронизации (это значит что не 1 синхросигнал, а 2)

2) Одноступенчатые динамические - в регистрах сдвига с однофазной системой синхронизации, в регистрах памяти, в счётчиках

3) Двухступенчатые статические - во всех регистрах и счётчиках.

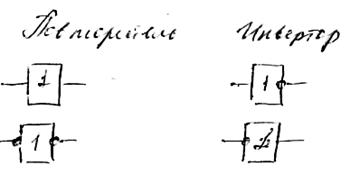

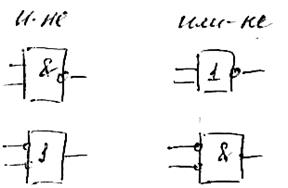

35. Соглашения положительной и отрицательной логики

H, L – высокий и низкий уровень

1) Положительной LOG 0 – L, LOG 1 – H

2) Отрицательной LOG 0 – H, LOG 1 – L

У входов и выходов могут быть разные соглашения.

1) Положительная

| X1 | X2 | Y |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

2) Отрицательная

| X1 | X2 | Y |

| 1 | 1 | 1 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 |