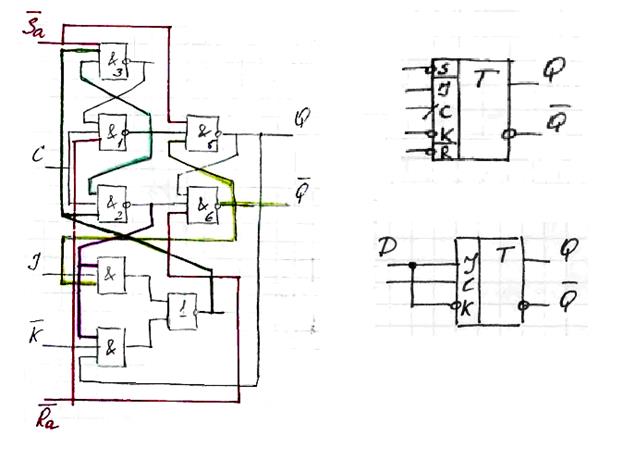

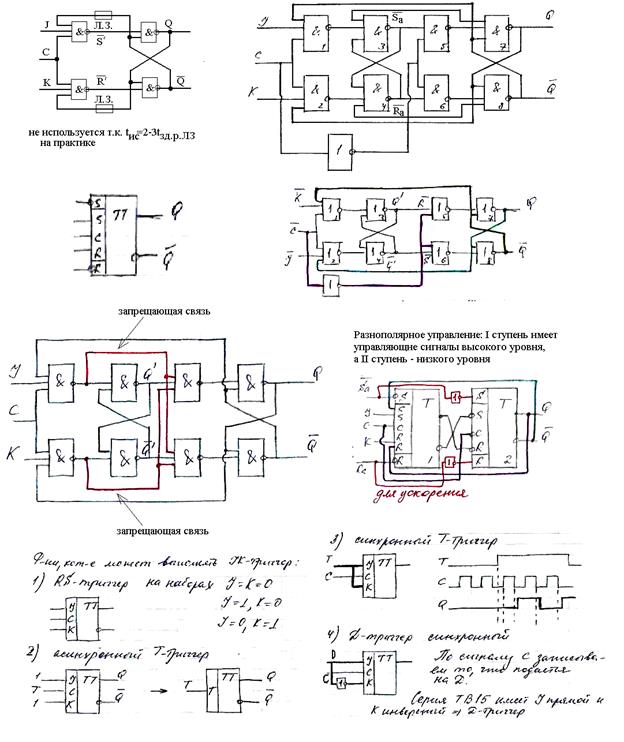

16. Синхронный JK-триггер с динамическим управлением записью

Из D-триггера получаем JK.

J=0, K=1 – режим хранения

J=0, K=0 – режим записи 0

J=1, K=1 – режим записи 1

J=1, K=0 – счетный режим

Если объединить входы J и K, то получится D-триггер

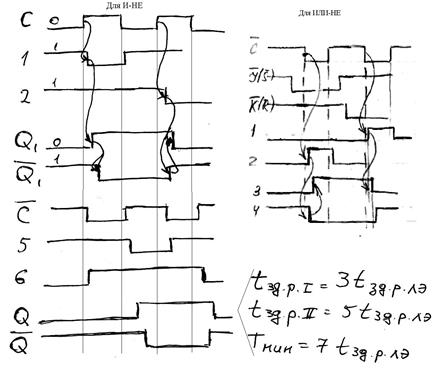

17. Синхронный JK-триггер со статическим управлением (двухступенчатый)

Двухступенчатые триггеры. При С=1 разрешается запись в 1ю ступень и запрещается перепись из 1й во 2ю. При С=0 происходит перепись информации из 1й ступени во 2ю, и перевод 1й ступени в режим хранения.

| C | J | K | Qn | Qn+1 | S* | R* |

В базисе И-НЕ: В базисе ИЛИ-НЕ:

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 0 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 1 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 1 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 0 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 0 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 1 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 1 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 0 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 0 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 1 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 0 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 1 | 1 | 0 | 0 | 1 |

Применение двухступенчатых статических триггеров: во всех регистрах и счетчиках.

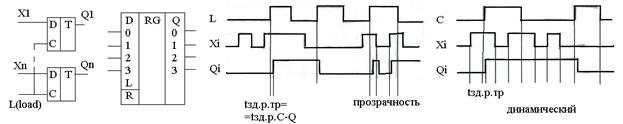

18. Регистры. Классификация, применение. Параллельные регистры

Регистр – это операционный узел, выполняющий функции записи, хранения, считывания информации, а также преобразования последовательного кода слова в параллельный и обратно, и выполняющий поразрядные логические операции (логическое сложение, умножение, исключающее или, инверсию).

Регистр представляет собой набор элементов памяти (триггеров), число которых равно или кратно числу разрядов преобразуемого слова, и комбинационных схем.

Регистры имеют независимые информационные входы для каждого разряда и общие входы управления.

Основной признак классификации: способ ввода/вывода:

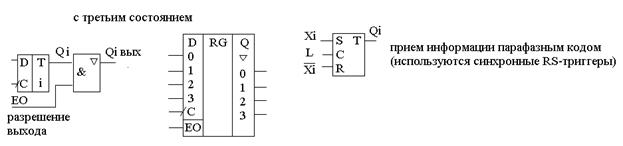

1) Параллельный. Все разряды слова передаются одновременно, за 1 такт T (простым или парафазным кодом:  -простой,

-простой,  -парафазный).

-парафазный).

2) Последовательный. Все разряды слова передаются последовательно во времени, каждый за 1 такт T. Время передачи nT.

3) Параллельно-последовательный способ. Слово разбивается на группы разрядов. Группы передаются параллельно, разряды в группах последовательно.

В зависимости от выполняемых функций и способа ввода/выводы:

1) регистры памяти (параллельные)

2) регистры сдвига (последовательные)

3) в интегральной схемотехнике имеются универсальные регистры (ввод, хранение, сдвиг). Они могут быть программно управляемы.

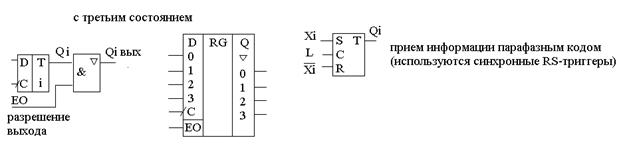

В регистрах используются D, DV, RS триггеры (JK не применяется, т.к. его функция избыточна для регистра). Чаще всего D.

Регистры могут иметь сложности цепей ввода и вывода: на входе может осуществляться мультиплексирование. Вывод может выполняться простым/обратным/парафазным кодом. Выход может иметь или три состояния или открытый коллектор.

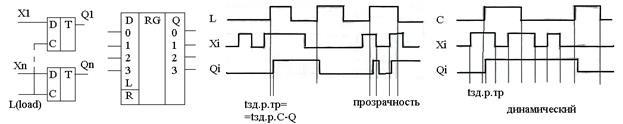

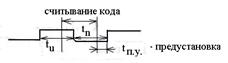

Регистры памяти (параллельные регистры). Запись, хранение, выдача информации. Для временного хранения информации в течении 1 или нескольких циклов работы устройства. Чаще всего с однофазным вводом на основе D-триггеров (как со статическим, так и с динамическим управлением записью).

Со статическим входом – прозрачный триггер. Обычно 4х или 8ми разрядные.

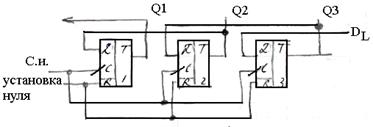

С динамическим управлением записью. Данные триггера непрозрачны. Вход R установки в начальное нулевое состояние – асинхронный. Это расширяет возможности регистра –возможна очистка регистра.

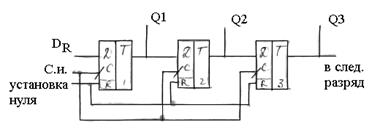

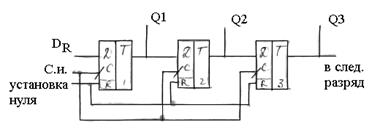

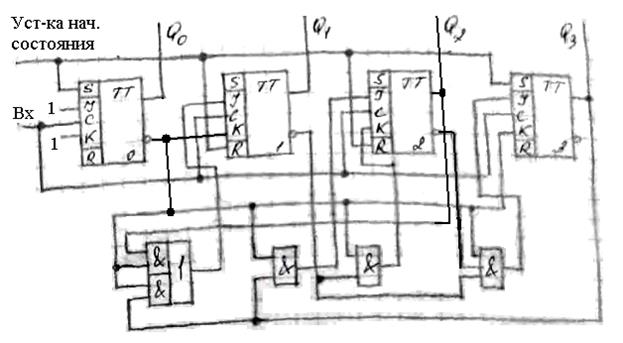

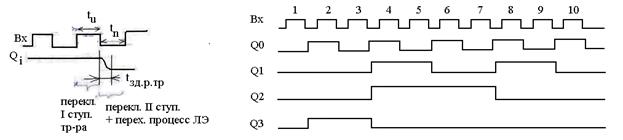

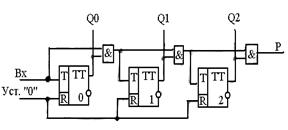

19. Регистры сдвига. Синтез, реализация ,временные диаграммы

Регистры сдвига строятся, как правило, или на триггерах с динамическим управлением записью (одноступенчатые), или на триггерах с двухступенчатым запоминанием информации. Регистры сдвига состоят из элементов памяти и комбинационных схем (для передачи информации из разряда в разряд). Как правило, схема однородная, кроме первого и последнего разрядов.

Регистры сдвига обычно строятся на D-триггерах. Сдвиг информации осуществляется тактовыми сигналами, поступающими на входы С всех триггеров регистра.

Таблица переходов i-го разряда.

| M |

|

|

|

|

M (Mode) – управляющий сигнал, задает режим сдвига М=0 – сдвиг вправо M=1 – сдвиг влево |

| 0 | 0 | X | X | 0 | |

| 0 | 1 | X | X | 1 | |

| 1 | X | X | 0 | 0 | |

| 1 | X | X | 1 | 1 |

при

при  - вправо

- вправо

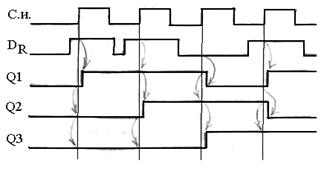

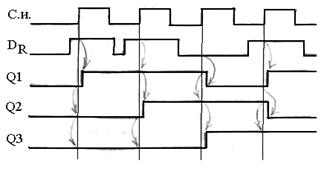

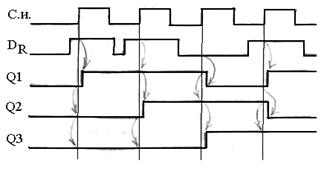

Синхроимпульсы (С.и.) поступают на входы С. Они обеспечивают сдвиг (в данном случае вправо).

(right)

(right)

За один такт – сдвиг на один разряд (за счет динамического управления записью)

За один такт – сдвиг на один разряд (за счет динамического управления записью)

Вход последовательный -

Выход параллельный -

Т.о. возможно преобразование последовательного кода в параллельный. Также код может сниматься последовательно с  за счет последовательного сдвига. Т.е. возможно преобразование параллельного кода в последовательный.

за счет последовательного сдвига. Т.е. возможно преобразование параллельного кода в последовательный.

Оценка быстродействия:  . Все разряды переключаются одновременно.

. Все разряды переключаются одновременно.

- влево

- влево

(left)

(left)

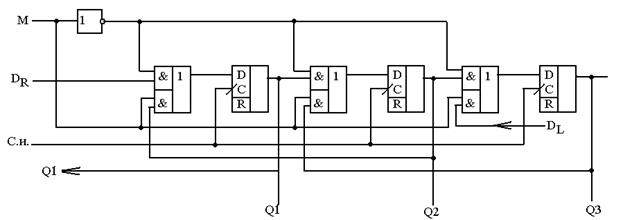

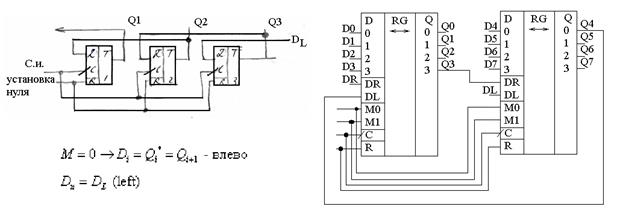

20. Реверсивные регистры сдвига. Синтез, реализация ,временные диаграммы.

Сдвиг информации осуществляется тактовыми сигналами, поступающими на входы С всех триггеров регистра.

Таблица переходов i-го разряда.

| M |

|

|

|

|

M (Mode) – управляющий сигнал, задает режим сдвига М=0 – сдвиг вправо M=1 – сдвиг влево |

| 0 | 0 | X | X | 0 | |

| 0 | 1 | X | X | 1 | |

| 1 | X | X | 0 | 0 | |

| 1 | X | X | 1 | 1 |

Со входом M  в обе стороны.

в обе стороны.

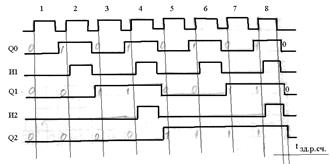

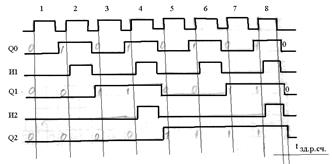

Временная диаграмма для сдвига вправо:

Быстродействие падает из-за использования элементов И-ИЛИ:

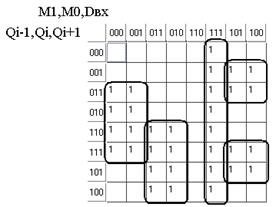

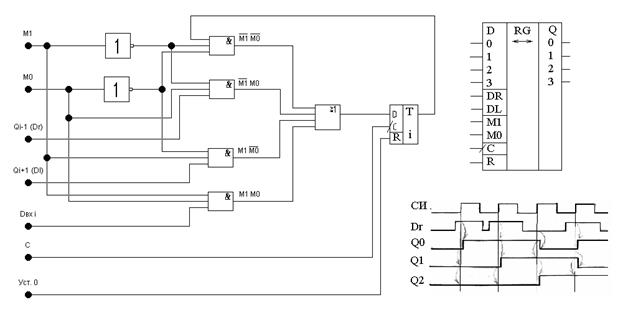

21. Универсальные регистры. Синтез, временные диаграммы

Основные микрооперации: 1) сдвиг влево, 2) сдвиг вправо, 3) загрузка начального слова, 4) хранение, 5) установка начального состояния.

Чтобы задать микрооперацию надо ввести управляющее слово. Это программируемый регистр M(mode). Два входа M1, M0 – управляющие слова.

| M1 | M0 | Dвх | Qi-1 | Qi | Qi+1 | Qi* |

| 0 | 0 | x | x | 0 | x | 0 |

| 0 | 0 | x | x | 1 | x | 1 |

| 0 | 1 | x | 0 | x | x | 0 |

| 0 | 1 | x | 1 | x | x | 1 |

| 1 | 0 | x | x | x | 0 | 0 |

| 1 | 0 | x | x | x | 1 | 1 |

| 1 | 1 | 0 | x | x | x | 0 |

| 1 | 1 | 1 | x | x | x | 1 |

| M1 | M0 | Микрооперация |

| 0 | 0 | Хранение |

| 0 | 1 | Сдвиг вправо |

| 1 | 0 | Сдвиг влево |

| 1 | 1 | Загрузка нач. слова |

Все микрооперации выполняются тактов. сигналом С

Таблица переходов универсального регистра сдвига (i-й разряд)

(1),(2),(3) – функции демультиплексирования

Установка в 0 может быть выполнена асинхронно (через R).

Входы DR и DL используются для наращивания разрядности.

P. S. В новых лекциях микрооперации были реализованы по другому. В принципе большой разницы нету, кто хочет, может переделать ответ под 11 – хранение, 00 – загрузка начального слова.

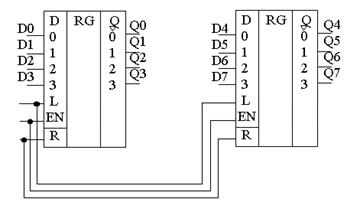

22. Наращивание //-ных регистров.

Регистры памяти (параллельные регистры). Запись, хранение, выдача информации. Для временного хранения информации в течении 1 или нескольких циклов работы устройства. Чаще всего с однофазным вводом на основе D-триггеров (как со статическим, так и с динамическим управлением записью).

Со статическим входом – прозрачный триггер. Обычно 4х или 8ми разрядные.

С динамическим управлением записью. Данные триггера непрозрачны. Вход R установки в начальное нулевое состояние – асинхронный. Это расширяет возможности регистра –возможна очистка регистра.

В секции параллельных регистров запараллеливают по С, по линии сброса в 0, и по другим управляющим сигналам.

23. Наращивание регистров сдвига

Регистры сдвига строятся, как правило, или на триггерах с динамическим управлением записью (одноступенчатые), или на триггерах с двухступенчатым запоминанием информации. Регистры сдвига состоят из элементов памяти и комбинационных схем (для передачи информации из разряда в разряд). Как правило, схема однородная, кроме первого и последнего разрядов.

Регистры сдвига обычно строятся на D-триггерах. Сдвиг информации осуществляется тактовыми сигналами, поступающими на входы С всех триггеров регистра.

Таблица переходов i-го разряда.

| M |

|

|

|

|

M (Mode) – управляющий сигнал, задает режим сдвига М=0 – сдвиг вправо M=1 – сдвиг влево

|

| 0 | 0 | X | X | 0 | |

| 0 | 1 | X | X | 1 | |

| 1 | X | X | 0 | 0 | |

| 1 | X | X | 1 | 1 |

Синхроимпульсы (С.и.) поступают на входы С. Они обеспечивают сдвиг (в данном случае вправо).

(right)

(right)

За один такт – сдвиг на один разряд (за счет динамического управления записью)

За один такт – сдвиг на один разряд (за счет динамического управления записью)

Вход последовательный -

Выход параллельный -

Т.о. возможно преобразование последовательного кода в параллельный. Также код может сниматься последовательно с  за счет последовательного сдвига. Т.е. возможно преобразование параллельного кода в последовательный.

за счет последовательного сдвига. Т.е. возможно преобразование параллельного кода в последовательный.

Оценка быстродействия:  . Все разряды переключаются одновременно.

. Все разряды переключаются одновременно.

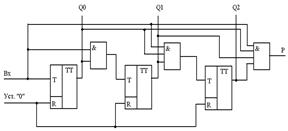

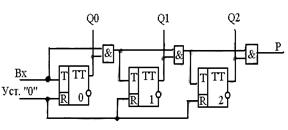

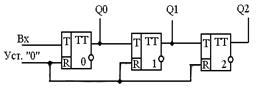

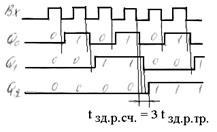

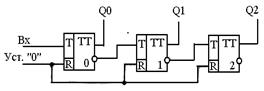

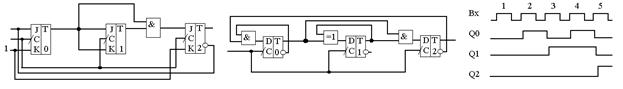

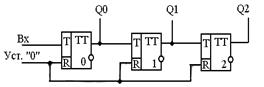

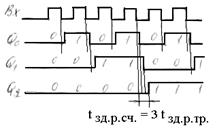

24. Асинхронный двоичный счетчик. Синтез, вр.диаграммы, параметры быстродействия. (на Т-триггерах)

Сам счет выполняется с помощью триггеров. Трехразрядный n=3.

| № | Q2 | Q1 | Q0 | Вх. | Q2* | Q1* | Q0* | T2 | T1 | T0 |

|

| Q2 | Q1 | Q0 | 0 | Q2 | Q1 | Q0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 2 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 3 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| 4 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 5 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| 6 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 7 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

Функции возбуждения триггеров счетчика – зависимости информационного (счетного) сигнала от входных сигналов счетчика и выходных сигналов разрядов счетчика.

,

,

| Q2,Q1

Q0,Вх |

00 |

01 |

11 |

10 |

| 00 |

|

|

|

|

| 01 |

|

|

|

|

| 11 | 1 | 1 | 1 | 1 |

| 10 |

|

|

|

|

,

,

Схема с параллельным переносом (быстрая) Временные диаграммы счетчика

Схема с параллельным переносом (быстрая) Временные диаграммы счетчика

Триггеры переключаются не одновременно. Время задержки распространения счета растет с ростом числа разрядов.  . Все разряды переключаются практически одновременно (

. Все разряды переключаются практически одновременно (  , то они почти равны).

, то они почти равны).

Счетчики выпускаются секциями ограниченной разрядности (4 шт. обычно), т.к. ЛЭ «И» не могут иметь неограниченное число входов. Такой счетчик является делителем частоты (

Счетчики выпускаются секциями ограниченной разрядности (4 шт. обычно), т.к. ЛЭ «И» не могут иметь неограниченное число входов. Такой счетчик является делителем частоты (  )

)

Счетчик со сквозным переносом:

Счетчик с последовательным переносом:

Если показания снимать с инверсных выходов, то получим вычитающий счетчик. Еще вычитающий счетчик можно получить, подавая сигнал на вход следующего разряда с инверсного выхода, снимать сигнал надо с прямого выхода.

25. Асинхронный двоично-десятичный счетчик. Синтез, вр.диаграммы, параметры быстродействия. (на Т-триггерах)

Двоично-десятичный счетчик – счетчик по mod 10.

| № | Q3 | Q2 | Q1 | Q0 | Q3* | Q2* | Q1* | Q0* | T3 | T2 | T1 | T0 |

|

| Q3 | Q2 | Q1 | Q0 | Q3 | Q2 | Q1 | Q0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 3 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 5 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 7 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 9 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

,

,  ,

,  ,

,  ,

,

| Q3,Q2

Q1,Q0 |

00 |

01 |

11 |

10 | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 |

| 00 |

|

| * |

| * | * | * | |||||||||

| 01 | 1 | 1 | * |

| * | * | 1 | * | 1 | |||||||

| 11 | 1 | 1 | * | * | 1 | 1 | * | * | 1 | * | * | * | * | |||

| 10 |

|

| * | * | * | * | * | * | * | * |

Схема с параллельным переносом (быстрая)

Триггеры переключаются не одновременно. Время задержки распространения счета растет с ростом числа разрядов.  . Все разряды переключаются практически одновременно (

. Все разряды переключаются практически одновременно (  , то они почти равны).

, то они почти равны).

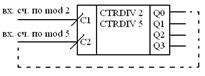

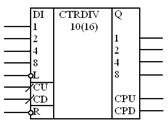

УГО

УГО

Может использоваться как счетчик по модулю 2 или 5. Чтобы получить по модулю 10 необходимо входы включить последовательно (пунктир).

CU – вход сложения CU  +1. CD – вход вычитания CD

+1. CD – вход вычитания CD  -1.

-1.

CU, CD – на одном из них импульс, на другом 1.

CPU, CPD – перенос при сложении/вычитании.

Асинхронная загрузка по L по входам 1, 2, 4, 8.

Наращивание данного счетчика производят подключением выходов CPU, CPD ко входам CU, CD следующего счетчика соответственно.

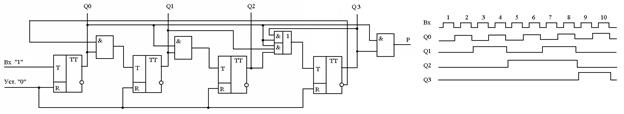

26. Синхронные счетчики по произвольному модулю (М=5,6,7,8,10,12 и т.д) . Синтез, временные диаграммы. (на JK- и D- триггерах как отдельный вариант), оценка быстродействия.

При синтезе счетчика задаются: 1) модуль счета; 2) может быть задан порядок изменения состояния; 3) может быть задан тип триггера. Если 2) не задается то по усмотрению разработчика (естественный). Требуется построить схему.

Основные положения методики:

- Определяется количество триггеров n.

Если модуль счета M и порядок счета естественный, то  , если порядок счета неестественный, то

, если порядок счета неестественный, то  , где M1 – наибольший номер состояния.

, где M1 – наибольший номер состояния.

Например 0,1,10,15,31,16,9,8,6,5,0, значит

- Составляется таблица переходов и функция возбуждения.

Пример: M=5 суммирующий с естественным порядком изм. сост.,

| N | Q2 | Q1 | Q0 | Q2* | Q1* | Q0* | J2 | K2 | J1 | K1 | J0 | K0 | D2 | D1 | D0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | a | 0 | a | 1 | a | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | a | 1 | a | a | 1 | 0 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | a | a | 0 | 1 | a | 0 | 1 | 1 |

| 3 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | a | a | 1 | a | 1 | 1 | 0 | 0 |

| 4 | 1 | 0 | 0 | 0 | 0 | 0 | a | 1 | 0 | a | 0 | a | 0 | 0 | 0 |

K0=1,  ,

,  ,

,  , K2=1,

, K2=1,

| Q2,Q1

Q0 |

00 |

01 |

11 |

10 | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 |

| 0 | 1 | 1 | b | 0 | a | 0 | b | a | 0 | a | b | 0 | 0 | 0 | b | a |

| 1 | a | a | b | b | a | 1 | b | b | 1 | a | b | b | 0 | 1 | b | b |

,

,  ,

,

| Q2,Q1

Q0 |

00 |

01 |

11 |

10 | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 |

| 0 | 0 | 0 | b | 0 | 0 | 1 | b | 0 | 1 | 1 | b | 0 |

| 1 | 0 | 1 | b | b | 1 | 0 | b | b | 0 | 0 | b | b |

Параметры быстродействия:

Обычно  в справочных данных.

в справочных данных.

27. Синхронные вычитающие счетчики по произвольному модулю(на JK- и D- триггерах). Синтез, вр. диаграммы, оценка быстродействия.

При синтезе счетчика задаются: 1) модуль счета; 2) может быть задан порядок изменения состояния; 3) может быть задан тип триггера. Если 2) не задается то по усмотрению разработчика (естественный). Требуется построить схему.

Основные положения методики: 1) Определяется количество триггеров n. Если модуль счета M и порядок счета естественный, то  , если порядок счета неестественный, то

, если порядок счета неестественный, то  , где M1 – наибольший номер состояния. Например 0,1,10,15,31,16,9,8,6,5,0, значит

, где M1 – наибольший номер состояния. Например 0,1,10,15,31,16,9,8,6,5,0, значит  . 2) Составляется таблица переходов и функция возбуждения. Пример: M=10 вычит. с ест. порядком изм. сост.,

. 2) Составляется таблица переходов и функция возбуждения. Пример: M=10 вычит. с ест. порядком изм. сост.,

| N | Q3 | Q2 | Q1 | Q0 | Q3* | Q2* | Q1* | Q0* | J3 | K3 | J2 | K2 | J1 | K1 | J0 | K0 | D3 | D2 | D1 | D0 |

| 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | a | 0 | 0 | a | 0 | a | a | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | a | 1 | 1 | a | 1 | a | 1 | a | 0 | 1 | 1 | 1 |

| 2 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | a | a | 0 | a | 0 | a | 1 | 0 | 1 | 1 | 0 |

| 3 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | a | a | 0 | a | 1 | 1 | a | 0 | 1 | 0 | 1 |

| 4 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | a | a | 0 | 0 | a | a | 1 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | a | a | 1 | 1 | a | 1 | a | 0 | 0 | 1 | 1 |

| 6 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | a | 0 | a | a | 0 | a | 1 | 0 | 0 | 1 | 0 |

| 7 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | a | 0 | a | a | 1 | 1 | a | 0 | 0 | 0 | 1 |

| 8 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | a | 0 | a | 0 | a | a | 1 | 0 | 0 | 0 | 0 |

| 9 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | a | 0 | a | 0 | a | 1 | a | 1 | 0 | 0 | 1 |

J0=1, K0=1, т.к. на картах Карно только 1,a(альфа),*(бета, не используемые состояния).

,

,  ,

,  ,

,

| Q3,Q2

Q1,Q0 |

00 |

01 |

11 |

10 | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 |

| 00 |

| 1 | * | 1 | a | a | * | a | a | * | 1 | a | 1 | * | a | |

| 01 |

|

| * |

| a | a | * | a | a | * | a | * | a | |||

| 11 | a | a | * | * | * | * | a | * | * | a | * | * | ||||

| 10 | a | a | * | * | 1 | 1 | * | * | a | * | * | a | * | * |

,

,

| Q3,Q2

Q1,Q0 |

00 |

01 |

11 |

10 | 00 | 01 | 11 | 10 |

| 00 | 1 |

| * | a | a | a | * | 1 |

| 01 |

|

| * | a | a | a | * | |

| 11 |

|

| * | * | a | a | * | * |

| 10 |

|

| * | * | a | a | * | * |

,

,  ,

,  ,

,

| Q3,Q2

Q1,Q0 |

00 |

01 |

11 |

10 | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 | 00 | 01 | 11 | 10 |

| 00 | 1 |

| * |

| * | 1 | 1 | * | 1 | 1 | 1 | * | 1 | |||

| 01 |

|

| * | 1 | 1 | * | * | * | ||||||||

| 11 |

|

| * | * | 1 | * | * | 1 | 1 | * | * | * | * | |||

| 10 |

|

| * | * | 1 | * | * | * | * | 1 | 1 | * | * |

При начальном состоянии как на схеме  - это 9.

- это 9.

К.С. – комбинационная схема (все ЛЭ)

К.С. – комбинационная схема (все ЛЭ)

28. Наращивание асинхронных счетчиков. Параметры быстродействия.

Сам счет выполняется с помощью триггеров. Трехразрядный n=3.

Таблица переходов и функций возбуждения.

| № | Q2 | Q1 | Q0 | Вх. | Q2* | Q1* | Q0* | T2 | T1 | T0 |

Функции возбуждения триггеров счетчика – зависимости информационного (счетного) сигнала от входных сигналов счетчика и выходных сигналов разрядов счетчика. |

|

| Q2 | Q1 | Q0 | 0 | Q2 | Q1 | Q0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | |

| 2 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | |

| 3 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | |

| 4 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | |

| 5 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | |

| 6 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | |

| 7 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

По таблице строим карты Карно, например для T1:

| Q2,Q1

Q0,Вх |

00 |

01 |

11 | 10 | По картам Карно получаем функции возбуждения триггеров счетчика:

|

| 00 |

|

|

| ||

| 01 |

|

|

| ||

| 11 | 1 | 1 | 1 | 1 | |

| 10 |

|

|

|

Параллельный перенос:

Схема с параллельным переносом (быстрая) Временные диаграммы счетчика

Схема с параллельным переносом (быстрая) Временные диаграммы счетчика

Триггеры переключаются не одновременно. Время задержки распространения счета растет с ростом числа разрядов.  . Все разряды переключаются практически одновременно (

. Все разряды переключаются практически одновременно (  , то они почти равны).

, то они почти равны).

Счетчики выпускаются секциями ограниченной разрядности (4 шт. обычно), т.к. ЛЭ «И» не могут иметь неограниченное число входов.

Счетчики выпускаются секциями ограниченной разрядности (4 шт. обычно), т.к. ЛЭ «И» не могут иметь неограниченное число входов.

Сквозной перенос:

Последовательный перенос:

Последовательный перенос:

Далее наращивание - подачей P на вх. T младш. триггера.