1. Классификация элементов ЭВМ, элементы, устройства, узлы (определения) 1

2. Основные требования к системе элементов. 1

3. Основные параметры элементов ЭВМ... 2

4. Основные характеристики элементов ЭВМ... 3

5. Базовый ЛЭ ТТЛ (серия 155) 3

6. Базовый ЛЭ ТТЛШ (серия К555) 4

7. Базовый ЛЭ ТТЛШ (серия К531) 4

8. ЛЭ с открытым коллектором. Достоинства, недостатки, применение. 5

9. ЛЭ с тремя состояниями выхода. Достоинства, недостатки, применение. 6

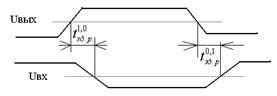

10. Двунаправленные элементы. Применение. Реализация. 7

11. Синхронный D-триггер со статическим управлением (одноступенчатый) 7

12. Синхронный D-триггер с двухступенчатым запоминанием информации. 8

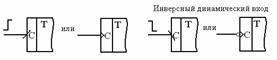

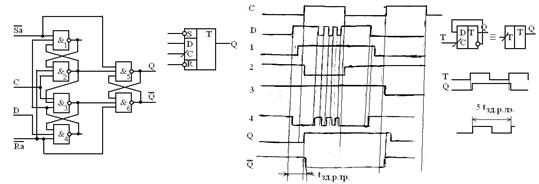

13. Синхронный D-триггер с динамическим управлением записью( одноступенчатый). 8

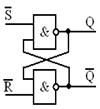

14. Синхронный Rs-триггер со статическим управлением (одноступенчатый). 9

15. Синхронный Rs-триггер со статическим управлением (двухступенчатый). 10

16. Синхронный JK-триггер с динамическим управлением записью.. 11

17. Синхронный JK-триггер со статическим управлением (двухступенчатый) 12

18. Регистры. Классификация, применение. Параллельные регистры.. 14

19. Регистры сдвига. Синтез, реализация ,временные диаграммы.. 15

20. Реверсивные регистры сдвига. Синтез, реализация ,временные диаграммы. 16

21. Универсальные регистры. Синтез, временные диаграммы.. 17

22. Наращивание //-ных регистров. 18

23. Наращивание регистров сдвига. 19

24. Асинхронный двоичный счетчик. Синтез, вр.диаграммы, параметры быстродействия. (на Т-триггерах) 20

25. Асинхронный двоично-десятичный счетчик. Синтез, вр.диаграммы, параметры быстродействия. (на Т-триггерах) 22

26. Синхронные счетчики по произвольному модулю (М=5,6,7,8,10,12 и т.д) . Синтез, временные диаграммы. (на JK- и D- триггерах как отдельный вариант), оценка быстродействия. 23

27. Синхронные вычитающие счетчики по произвольному модулю(на JK- и D- триггерах). Синтез, вр. диаграммы, оценка быстродействия. 24

28. Наращивание асинхронных счетчиков. Параметры быстродействия. 26

29. Наращивание синхронных счетчиков. Параметры быстродействия. 28

30. Классификация счетчиков, основные параметры.. 30

31. Вычитающие двоичные и двоично-десятичные счетчики асинхронного и синхронного типа. 31

32. Безвентильные счетчики (асинхронные счетчики по произвольному модулю). 33

33. Базовый ЛЭ ТТЛШ (серия 1531) 35

34. Двухтактные регистры сдвига. 36

35. Соглашения положительной и отрицательной логики. 36

1. Классификация элементов ЭВМ, элементы, устройства, узлы (определения)

Элемент ЭВМ – наименьшая функциональная часть, выполняющая определенную логическую или запоминающую функцию и используемая при логическом проектировании и конструктивном выполнении ЭВМ.

ФУ (узел) – часть ЭВМ, выполняющая определенную микрооперацию над словом или словами определенной разрядности, и состоящая из электрически связанных элементов.

Устройство ЭВМ – часть ЭВМ, выполняющая вполне определенные функции обработки информации, и состоящая из элементов и узлов ЭВМ.

Классификация элементов ЭВМ.

1) по форме представления информации: аналоговая (с помощью множества значений физической величины) и дискретная (конечным множеством значений-уровней физической величины). Частный случай дискретного – цифровой элемент, который оперирует с цифровым сигналом (который имеет 2 уровня представления).

2) по функциональному назначению: логические (выполняют элементарные логические функции), запоминающие (выполняют функции запоминания, хранения и регенерации информации. В ЭВМ это часто триггеры, магнитные и оптические среды, конденсаторы) и вспомогательные элементы.

3) по виду электрических сигналов: потенциальные(входные и выходные сигналы - потенциальные), импульсные(вх. и вых. сигн. - импульсные), импульсно-потенциальные(входные как импульсные, так и потенциальные, выходные – только импульсные), динамические(логическая единица отображается пачкой импульсов, ноль – отсутствием импульсов) и фазовые(сигналы могут иметь разные фазы гармонических сигналов для изображения 0 и 1, например синусоида и косинусоида).

4) по типу основного активного электро-радио-элемента: на биполярных и униполярных транзисторах.

5) по реализуемой логической функции различают логические элементы И(конъюнктор), ИЛИ(дизъюнктор), НЕ(инвертор), И-НЕ(штрих Шеффера), ИЛИ-НЕ(стрелка Пирса), И-ИЛИ-НЕ и другие…

2. Основные требования к системе элементов

Система элементов – совокупность элементов, предназначенных для совместного использования, имеющих единое питание, едино констр-технологическое исполнение и отвечающая требования функциональной и технической полноты и совместимости входных и выходных сигналов.

1) Функциональная полнота

2) Физическая полнота(система должна включать усилители, преобразователи, индикаторы, генераторы, и т.п. вспомогательные элементы)

3) Совместимость входных и выходных сигналов (выходными сигналами одного элемента можно управлять или переключать состояния другого элемента).

Т.к. сейчас элементы ЭВМ выполняются в интегральном исполнении, то степень сложности ИМС оценивается с помощью степени интеграции и функциональной сложности.

Т.к. сейчас элементы ЭВМ выполняются в интегральном исполнении, то степень сложности ИМС оценивается с помощью степени интеграции и функциональной сложности.

(I, II, III и т.д. степени интеграции)

(I, II, III и т.д. степени интеграции)

(1-МИС, 2-СИС, 3,4-БИС, >5-СБИС)

(1-МИС, 2-СИС, 3,4-БИС, >5-СБИС)

3. Основные параметры элементов ЭВМ

Параметры определяют качество ИМС (быстродействие, надежность, стоимость и т.д.). Сами параметры определяются по характеристикам элементов.

I ) Статические (в состоянии логического «0» или «1»)

Параметры напряжения:

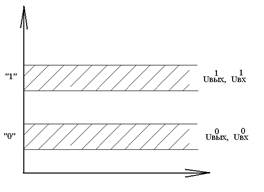

1) входные напряжения логического «0» и «1»:

2) выходные напряжения логического «0» и «1»:

3) пороговое напряжение:  - это такое напряжение, при котором начинается переключение ЛЭ из одного состояния в другое

- это такое напряжение, при котором начинается переключение ЛЭ из одного состояния в другое

4) логический перепад:

5) напряжение допустимой помехи:  , прикладывающееся ко входу и не изменяющее логическое состояние элемента. Характеризуют способность элемента противостоять помехам.

, прикладывающееся ко входу и не изменяющее логическое состояние элемента. Характеризуют способность элемента противостоять помехам.

Токовые параметры:

1) входные токи логического «0» и «1»:  - это такие токи, которые находятся во входной цепи ЛЭ, когда на вход элемента подается

- это такие токи, которые находятся во входной цепи ЛЭ, когда на вход элемента подается  соответственно

соответственно

2) выходные токи логического «0» и «1»:

Входные и выходные токи позволяют определить нагрузочную способность логических элементов.

3) ток выходной цепи ЛЭ с открытым коллектором  (до 250 мкА в ТТЛ)

(до 250 мкА в ТТЛ)

4) ток выходной цепи ЛЭ в состоянии Z (в 3м состоянии, высокий импеданс)

5) потребляемые токи в состоянии логического «0» и «1»:

Коэффициент нагрузочной способности (коэффициент разветвления по выходу)

Коэффициент объединения по входу  определяет количество входов ЛЭ

определяет количество входов ЛЭ

Коэффициент объединения по выходу  . Некоторые элементы допускают объединение по выходу, но их количество ограничено, т.к. при увеличении количество объединенных выходов, увеличивается емкость узла, а значит ухудшаются свойства

. Некоторые элементы допускают объединение по выходу, но их количество ограничено, т.к. при увеличении количество объединенных выходов, увеличивается емкость узла, а значит ухудшаются свойства

Потребляемая мощность

Напряжение питания

II ) Динамические (в процессе переключения)

1)  времена задержек распространения

времена задержек распространения

2) работа переключения

III ) Параметры надежности

1) интенсивность отказов  (10-8-10-9 1/ч), где N - число микросхем, поставленных на испытания, t – время испытаний, n – число ИМС, вышедших из строя

(10-8-10-9 1/ч), где N - число микросхем, поставленных на испытания, t – время испытаний, n – число ИМС, вышедших из строя

2) время наработки на отказ

3) вероятность безотказной работы

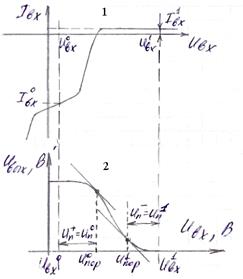

4. Основные характеристики элементов ЭВМ

I ) Статические

I ) Статические

1) входная  . Измеряется для одного входа, а на остальные подается

. Измеряется для одного входа, а на остальные подается  или

или  при максимальной нагрузочной способности.

при максимальной нагрузочной способности.

2) передаточная

3) выходная  . Снимается для обоих состояний ЛЭ.

. Снимается для обоих состояний ЛЭ.

II ) Динамические

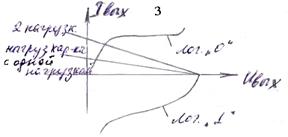

1) Нагрузочная характеристика

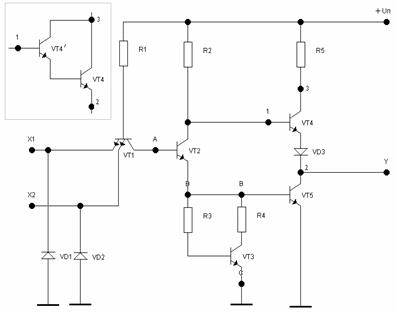

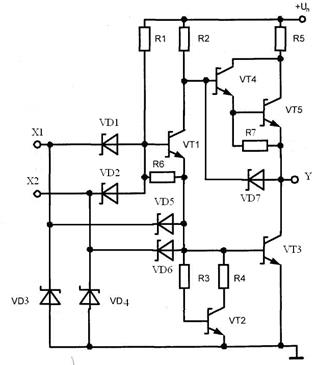

5. Базовый ЛЭ ТТЛ (серия 155)

VT1+R1 – функция «И» (т. А)

VT1+R1 – функция «И» (т. А)

VT2+R2+R3 – фазоинверсный каскад между т.В и т.С (корректирующая цепь)

VT4 – в режиме эмиттерного повторителя

VD1 и VD2 – антизвонные

VD3 – для надежн. запир. VT4

1)

- низкий уровень:

- низкий уровень:

VT2 закрыт, VT4 открыт, VT1 открыт

2)

- высокий уровень:

- высокий уровень:

VT1 – инверсный активный режим, VT2, VT3, VT5 открыты, VT5 насыщение.

3)  .

.  - для ограничения сквозного тока при переключении.

- для ограничения сквозного тока при переключении.

Вместо VT4 и VD3 можно включить схему Дарлингтона (на составных транзисторах). Тогда коэффициент усиления  .

.

К133, К155 – имена на обычных транзисторах

К134, К136 – пониженная потребляемая мощность

К130, К131 – мощные серии (повышенное быстродействие)

Этот ЛЭ реализует функцию И-НЕ (К155ЛА3)

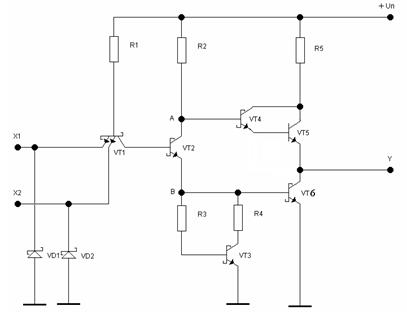

6. Базовый ЛЭ ТТЛШ (серия К555)

Транзисторы Шоттки отличаются от обычных тем, что они не входят в глубокое насыщение, следовательно, в их базах в открытом состоянии накапливается мало носителей заряда, и в результате время их рассасывания меньше обычного.

Элементы ТТЛШ работают в ненасыщенном режиме (следовательно повышается быстродействие) и имеют низкую потребляемую мощность (в 4-5 раз).

Базовый элемент К555ЛА3.Функция И-НЕ.

VD1, VD2, R1 – функция И.

Остальное – функция НЕ.

При подаче на все входные выводы элемента напряжения высокого уровня парные диоды VD1, VD2 входных ключей на диодах смещаются в обратном направлении. Поэтому ток резистора R1 насыщает транзисторы VT1 и VT3, формируя на выходе элемента сигнал низкого уровня. Если хотя бы на один вход схемы подано низкое напряжения, соответствующий диод смещается в прямом направлении. Ток резистора R1 замыкается на общую шину, минуя эмиттерные переходы транзисторов VT1 и VT3 (они закрываются). При этом ток резистора R2 насыщает составной транзистор VT4, VT5, формируя на выходе напряжение высокого уровня.

7. Базовый ЛЭ ТТЛШ (серия К531)

Транзисторы Шоттки отличаются от обычных тем, что они не входят в глубокое насыщение, следовательно, в их базах в открытом состоянии накапливается мало носителей заряда, и в результате время их рассасывания меньше обычного.

Элементы ТТЛШ работают в ненасыщенном режиме (следовательно повышается быстродействие) и имеют низкую потребляемую мощность (в 4-5 раз). К531 – ЛЭ специального применения(с транзисторами Шотки), функция И-НЕ.

Элементы ТТЛШ работают в ненасыщенном режиме (следовательно повышается быстродействие) и имеют низкую потребляемую мощность (в 4-5 раз). К531 – ЛЭ специального применения(с транзисторами Шотки), функция И-НЕ.

А,В – для расширения функции

VT5 – не Шотки! т.к. он и так не входит в режим насыщения.

VT1+R1 – функция «И»

VT2+R2+R3 – фазоинверсный каскад (корректирующая цепь)

VD1 и VD2 – антизвонные

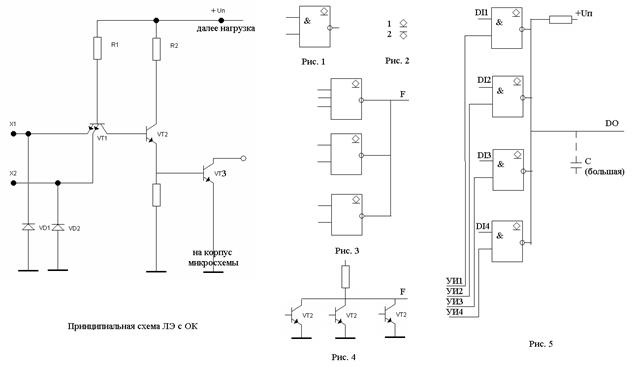

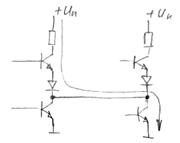

8. ЛЭ с открытым коллектором. Достоинства, недостатки, применение

Обычно VT3 более мощный чем остальные, поэтому элементы с ОК – с повышенной нагрузочной способностью (  ).

).

У обычных схем  , с ОК -

, с ОК -  и т.д.(повышенное допустимое напряжение коллектора у VT3).

и т.д.(повышенное допустимое напряжение коллектора у VT3).

ЛЭ с ОК допускают непосредственное объединение по выходу – операция «монтажное ИЛИ».

На рис. 1 показано условное графическое изображение ЛЭ с ОК. На рис. 2: 1 – ОК для n-p-n транзисторов, ОЭ для p-n-p, 2 - ОЭ для n-p-n транзисторов, ОК для p-n-p.

Если ЛЭ реализуют функции F1, F2, F3, то при объединении этих ЛЭ по выходу  на рис. 3 и рис. 4(это если элементы инвертирующие).

на рис. 3 и рис. 4(это если элементы инвертирующие).

Аналог в КМОП – с открытым стоком. Применение: для работы на нестандартную нагрузку и в приемопередатчиках для взаимного соединения нескольких устройств вычислительной техники. ЛЭ с повышенной нагрузочной способностью называются драйверы. Элементы, которые являются драйверами и приемопередатчиками, называются бус-драйверы.

На рис. 5 односторонняя передача информации с нескольких источников на шину: DI – data input – источник, DO – data output – шина, УИ – управляющий импульс.

Недостаток ЛЭ с ОК: меньшее быстродействие по сравнению с элементами со стандартным выходом (увеличена задержка распространения).

Разряд быстрый т.к. через транзистор, заряд медленный т.к. не через транзистор, а через сопротивление. У транзисторов сопротивление мало. через них все идет быстро.

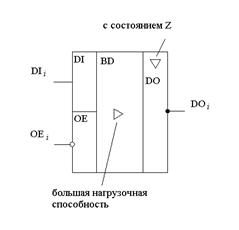

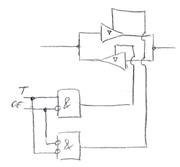

9. ЛЭ с тремя состояниями выхода. Достоинства, недостатки, применение

К таким элементам относятся некоторые ЛЭ (мало) и шинные драйверы (приемопередатчики). Обладают повышенной нагрузочной способностью. Допускают объединение выходов («монтажное ИЛИ»). В отличие от элементов с открытым коллектором допустимо подключение к выходу только одного канала с состоянием Z.

3 выходных состояния: 0, 1, Z (высокое  , высокий импеданс).

, высокий импеданс).

Примеры: ЛП8 – шинный драйвер, К155ЛП8, К555ЛП8, К533ЛП8, КР1533ЛП8 и др.

Выход разрешен, если OE = 0

OE – output enable – разрешение выхода.

«enable Z»

Аналог – ЛП5 (8 штук, каждые 4 имеют общий сигнал управления).

В драйверах вместо ЛЭ с ОК можно применять элементы с 3 состояниями. Но существует особенность в управлении: если применяются элементы с состоянием Z, то должен быть включен только один канал (иначе происходит перегрев выходных транзисторов).

Перегрев – см. рис.!

Перегрев – см. рис.!

Т.е. не должно быть

Достоинство: более высокое быстродействие (малое выходное сопротивление и у верхнего, и у нижнего плеча).

Управляющий импульс (OE) генерирует обычно дешифратор.

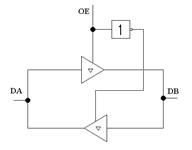

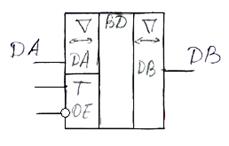

10. Двунаправленные элементы. Применение. Реализация

Западное обозначение драйверов. Если информация передается справа налево, снизу вверх, то надо рисовать стрелки.

Если двунаправленный:

Противофазное управление:

OE=1: A->B

OE=0: B->A (рисунок слева)

Пример: АП6 – управляющие сигналы T (направление передачи), OE. (рисунок справа)

| T | OE | Напр-ие пер-чи | Примеч. |

|

| 0 | 0 | DA->DB | DA - вход | |

| 1 | 0 | DB->DA | DB – вход | |

| x | 1 | DA=DB=Z |

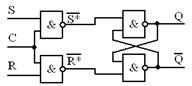

11. Синхронный D-триггер со статическим управлением (одноступенчатый)

При С=0 триггер находится в режиме хранения информации, при С=1 переключается как асинхронный триггер соответствующего типа.

| C | D | Qn | Qn+1 | S* | R* |

|

| 0 | 0 | 0 | 0 | 0 |

| |

| 0 | 0 | 1 | 1 |

| 0 | |

| 0 | 1 | 0 | 0 | 0 |

| |

| 0 | 1 | 1 | 1 |

| 0 | |

| 1 | 0 | 0 | 0 | 0 |

| |

| 1 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 1 |

| 0 |

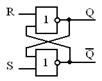

Еще можно использовать схему асинхронного RS-триггера с прямыми входами в базисе ИЛИ-НЕ:

Еще можно использовать схему асинхронного RS-триггера с прямыми входами в базисе ИЛИ-НЕ:

Применение одноступенчатых статических триггеров: в регистрах памяти, в регистрах сдвига, только если используется 2-х фазная система синхронизации (это значит что не 1 синхросигнал, а 2)

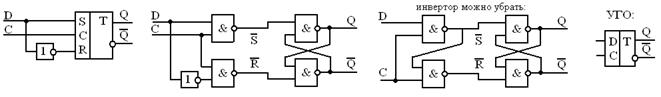

12. Синхронный D-триггер с двухступенчатым запоминанием информации.

В двухступенчатых триггерах входная и выходная ступени тактируются «антисинхронно», прием информации разрешается в них поочередно. Вследствие этого отсутствует режим прозрачности триггера при любом уровне синхросигнала, что позволяет реализовать любые типы триггеров, свободные от режимов генерации, и дает возможность построения си7хронных автоматов без опасных временных состязаний. Однако, их схемы более сложные, чем с динамическим входом, а быстродействие несколько ниже.

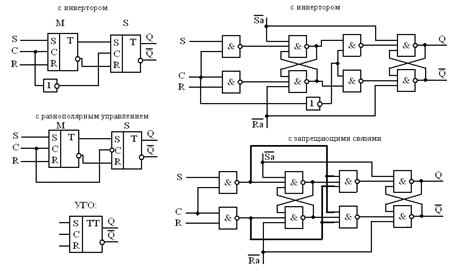

Двухступенчатые триггеры строятся несколькими способами: с инвертором, с разнополярным управлением ступенями, с запрещающими связями. Первая ступень – всегда D-триггер.

M – Master, S- Slave.

При С=0 перепись информации из первой ступени во вторую и перевод первой ступени в режим хранения. При С=1 разрешена запись в первую ступень и запрещена перепись из первой ступени во вторую.

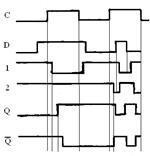

13. Синхронный D-триггер с динамическим управлением записью( одноступенчатый).

Строятся как по одноступенчатым, так и по двухступенчатым схемам. Принцип работы – переключаются перепадом сигнала С.

Строятся как по одноступенчатым, так и по двухступенчатым схемам. Принцип работы – переключаются перепадом сигнала С.

Чувствительность к изменению состояния сохраняется в течении  .

.

Время предустановки – время, в течение которого перед переключением, триггер должен быть предустановлен.

Может выполнять функции D триггера и T триггера.

Может выполнять функции D триггера и T триггера.

- работа в сч. режиме.

- работа в сч. режиме.

Триггер на 3-х RS-триггерах. 5,6 – осн. триггер (ЗЯ).

D-триггер - ТМ2: К155ТМ2, К555ТМ2, КР1533ТМ2. В корпусе МС расположено 2 триггера (14 выводов).

14. Синхронный Rs-триггер со статическим управлением (одноступенчатый).

При С=0 триггер находится в режиме хранения информации, при С=1 переключается как асинхронный триггер соответствующего типа. В качестве ЗЯ – асинхронный RS–триггер.

| SR

Q |

00 |

01 |

11 | 10 |

В базисе И-НЕ: В базисе ИЛИ-НЕ: |

| 0 |

|

| X | 1 | |

| 1 | 1 |

| X | 1 |

Реализация ЗЯ в базисах И-НЕ, ИЛИ-НЕ:

| C | S | R | Qn | Qn+1 | S* | R* |

В базисе И-НЕ: В базисе ИЛИ-НЕ: | ||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 0 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 1 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 1 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 0 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 0 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 1 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 1 | 1 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 0 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 0 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 1 | 0 | 0 | 0 |

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 0 | 1 | 1 |

| 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 1 | 0 | X |

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| 1 | 1 | 1 | 1 | X |

|

|

Реализация СУ в базисах И-НЕ, ИЛИ-НЕ:

Реализация синхронного RS-триггера со статическим управлением в базисах И-НЕ, ИЛИ-НЕ:

Комбинируя различным образом СУ и ЗЯ в различных вариантах реализации можно получить реализации синхронного RS-триггера со статическим управлением комбинированным образом (с использованием ЛЭ обоих типов: И-НЕ, ИЛИ-НЕ).

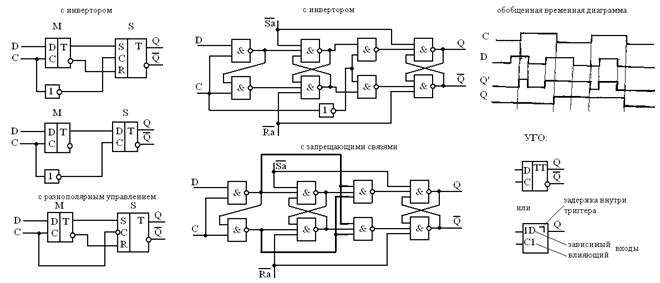

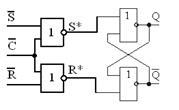

15. Синхронный Rs-триггер со статическим управлением (двухступенчатый).

В двухступенчатых триггерах входная и выходная ступени тактируются «антисинхронно», прием информации разрешается в них поочередно. Вследствие этого отсутствует режим прозрачности триггера при любом уровне синхросигнала, что позволяет реализовать любые типы триггеров, свободные от режимов генерации, и дает возможность построения си7хронных автоматов без опасных временных состязаний. Однако, их схемы более сложные, чем с динамическим входом, а быстродействие несколько ниже.

Двухступенчатые триггеры строятся несколькими способами: с инвертором, с разнополярным управлением ступенями, с запрещающими связями. В данном случае обе ступени – синхронные RS-триггеры.

MS-триггера (триггер типа Flip-Flop)

MS-триггера (триггер типа Flip-Flop)

M – Master, S- Slave.

При С=0 перепись информации из первой ступени во вторую и перевод первой ступени в режим хранения. При С=1 разрешена запись в первую ступень и запрещена перепись из первой ступени во вторую.

Применение двухступенчатых статических триггеров: во всех регистрах и счетчиках.

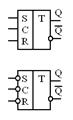

Обозначение

Обозначение