Организация внутренней памяти данных.

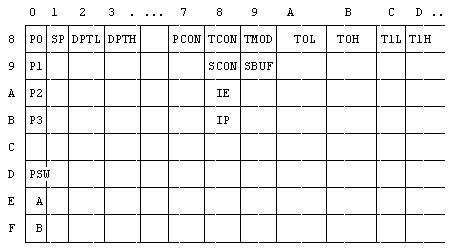

Пространство DSEG включает в себя 256 ячеек памяти, часть из которых является одновременно элементами других пространств. Так, первые 32 байта ОЗУ занимают 4 банка. Служебные регистры, порты ввода/вывода, таймеры, аккумуляторы и др. так же совмещены с ячейками памяти и полями битового сегмента. Это дает возможность обращения к одному физическому объекту разными способами. Так, к ячейке DSEG[E0] можно обратиться по прямому и косвенному адресу, обратиться как к аккумулятору A и как к полю BSEG[E0..E7] (к каждому биту в отдельности).

Рис. 9.11. Пространство внутренней памяти данных DSEG

Память программ адресуется PC[15:0] и может составлять до 64К байт, причем младшие 4 К могут располагаться непосредственно на кристалле, а остальная память внешнее ЗУ. С точки зрения программиста внешняя и внутренняя память программ представляют единое адресное пространство. Имеются "особые точки"

CSEG:

RESET 0000h - стартовый адрес;

EXTI0 0003h - внешнее прерывание 0;

TIMER0 000Bh - прерывание от таймера/счетчика T0;

EXTI1 0013h - внешнее прерывание 1;

TIMER1 001Bh - прерывание от таймера/счетчика T1;

SINT 0023h - прерывание последовательного порта;

Машинные циклы и синхронизация микро-ЭВМ

Питание МК51 осуществляется от одного источника +5В. Кварцевый резонатор 3,5..12 МГц подключается к выводам Х1, Х2; возможно подключение внешнего тактового генератора через Х1.

OSC/2 - основная внутренняя тактовая частота CLK. Первая половина периода CLK фаза P1, вторая - P2. Каждый машинный цикл состоит из шести периодов CLK: состояний S1, S2, .. S6 или двенадцати периодов OSC, называемых фазами S1P1, S1P2, S2P1, .. S6P, S6P2. Каждый машинный цикл сопровождается генерацией двух стробов ALE длительностью в один период CLK - S1P2..S2P1, S4P2.. S5P1.

Командный цикл (КЦ) содержит один или несколько машинных циклов (МЦ) и отсчитывается от S1P1. По фазе S1P2 в IR фиксируется код операции, второй байт двухбайтовой команды читается в S4P2 того же МЦ, третий байт трехбайтовой - в S1P2 следующего МЦ. Таким образом, для ввода каждого байта команды требуется один полуцикл.

Во время всех оставшихся полуциклов в фазах S1P2 и S4P2 читается код операции следующей размещенной в памяти команды, однако он не помещается в IR и не инкрементируется PC. Текущий КЦ всегда завершается в S6P2. Вслед за этим начинается S1, в котором в IR вводится новый байт.

Обращение к внешней памяти данных XSEG по команде MOVX требует второго МЦ, в котором не вырабатывается первый строб ALE. На рис. 3.7 приведена временная диаграмма обращения к XSEG.

Для приведение МК51 в исходное состояние необходимо подать на вход RST импульс H-уровня длительностью не менее 24 периодов OSC (два МЦ) при условии что генератор запущен.

Внешние устройства МК51

К "внешним" устройствам МК51 отнесем:

· 4 параллельных двунаправленных порта ввода/вывода P0..P3;

· буфер SBUF и регистр управления SCON последовательного канала;

· таймеры/счетчики T0, T1, их регистр управления TCON и регистр режимов TMOD;

· регистры управления подсистемой прерываний: регистр приоритетов IP и регистр маски IE;

· регистр управления машиной PCON.

В состав МК51 входит дуплексный последовательный канал связи с буферизацией, который может быть запрограммирован для работы в одном из четырех режимов:

· режим "0" - синхронный ввод/вывод с частотой OSC/12;

· режим "1" - асинхронный с 8-бит. кадром, частота k*f;

· режим "2" - асинхронный с 9-бит. кадром, частота k*OSC/32;

· режим "3" - асинхронный с 9-бит. кадром, частота k*f; где k {1, 1/2}, f - частота переполнения T1 (FOV), деленная на 16.