Машинные циклы i8086 в минимальном и максимальном режимах

Временные диаграммы работы МП i8086 в минимальном режиме представлены на Рис 9.5. и Рис. 9.6

Рис.9.5. Минимальный режим – цикл ЧТЕНИЕ

Рис.9.6. Минимальный режим – цикл ЗАПИСЬ

Цикл начинается с формирования в T1 сигнала M/IO, определяющего тип устройства - память или ВУ, с которым осуществляется обмен данными. Длительность сигнала M/IO равна длительности цикла шины, и он используется для селекции адреса устройств. В T1 и в начале T2 МП выдает адрес A[19:16] и A[15:0] и сигнал BHE, который вместе с A0 определяет передачу слова или одного из байтов. По спаду строба ALE адрес фиксируется во внешних регистрах-защелках.

В такте T2 происходит переключение шин: на выводы A[19:16]/ ST[6:3] поступают сигналы состояния; выводы A/D[15:0] в цикле ЧТЕНИЕ переводятся в высокоимпедансное состояние, а в цикле ЗАПИСЬ - на них выдаются данные, предназначенные для записи в устройство.

Циклы ЧТЕНИЕ и ЗАПИСЬ отличаются не только активными значениями сигналов RD и WR и состоянием сигнала OP/IP, но и тем, что в цикле ЗАПИСЬ сигналы DEN и WR становятся активными раньше и имеют большую длительность, чем в цикле ЧТЕНИЕ.

В максимальном режиме изменяются значения восьми управляющих сигналов МП, на основании которых системный контроллер К1810ВГ88 формирует системные управляющие сигналы. Временные диаграммы работы i8086 в максимальном режиме представлены на Рис. 9.7.

Код состояния S[2:0] выдается по срезу CLK в последнем такте предшествующего цикла, которым может быть T4 или TI. В такте T1 контроллер формирует строб ALE и устанавливает необходимый уровень на выходе OP/IP (DT/R). В такте T2 начинается формирование DEN, который в отличие от минимального режима имеет активный высокий уровень. Контроллер. .ВГ88 формирует так же MRDC\, IORC\, AMWC\, AIOWC\. Последние два - сигналы опережающей записи обеспечивают более длительный импульс записи, что может потребоваться для некоторых устройств. Следует помнить, что сигналы опережающей записи не гарантируют установку данных по началу импульса записи. При разработке контроллера. .ВГ88 предполагалось, что шина данных системы буферизована, поэтому сигналы MRDC, IORC, AMWC, AIOWC начинают формироваться еще до того, как МП переведет шину в третье состояние. Поэтому эти сигналы не должны подаваться на те устройства, которые подключены непосредственно к мультиплексированной шине A/D. На Рис. 9. в рамки помещены сигналы, которые формирует системный контроллер К1810ВГ88.

При работе в асинхронном режиме между тактами T3 и T4 могут появиться один или несколько тактов ожидания Tw, в течении которых МП удерживает в активном состоянии выводы ST2..ST0, так что контроллер сохраняет управление шиной в течение любого числа тактов ожидания Tw. Сигнал направления передачи OP/IP\, передаваемый на шинные формирователи (ШФ), устанавливается в такте T1, но работа ШФ не разрешается до появления сигнала DEN\ = 0 в такте T2. Строб данных DEN\ заканчивается в такте T4, что обеспечивает отключение ШФ до начала следующего цикла шины.

Рис.9.7. Временные диаграммы МЦ i8086 в максимальном режиме

Структура микропроцессорных модулей на базе микропроцессора i8086

Структура процессорных модулей на базе МП i8086 существенно зависит от выбранного режима работы МП.

Процессорный модуль, представленный на рис. 9.8, работает аналогично процессорному модулю на базе i8080, но управляет памятью большего объема и может осуществлять обмен двухбайтовыми словами.

Рис.9.8. Процессорный модуль на базе 8086 в минимальном режиме

Максимальный режим предполагает наличие в системе нескольких равноправных задатчиков, работающих на общую шину. При этом возможны варианты организации системы с одной системной шиной или с системной шиной и шиной ввода/вывода. Управление шинами осуществляется специализированными БИС: контроллером шины и арбитром шины.

На Рис. 9.9 показана однопроцессорная конфигурация с системной шиной (СШ), представленной линиями адреса AB[15:0], линиями данных DB[19:0] и линиями управления: MRDC\, MWTC\, AMWTC\, IORC\, IOWC\, AIOWC\, INTA\.

Рис. 9.9. Однопроцессорная конфигурация для максимального режима

Однокристальные микро-эвм типа МК51

МК51 это серия с ядром 80С51В. странах СНГ МК51 выпускаются на базе n-МОП технологии (серия 1816) и КМОП технологии (серия 1830).

Структура МК51

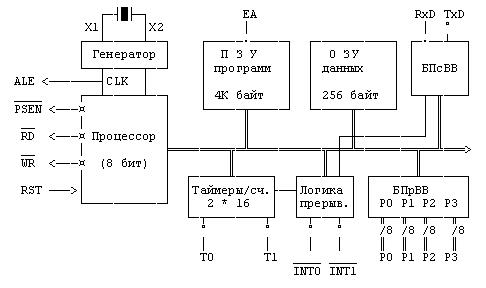

Рис. 9.10. Структура МК51

В МК51 используются следующие сигналы:

ALE - строб адреса;

PSEN\ - строб чтения внешней памяти программ;

RD\,WR\- стробы чтения и записи внешней памяти данных;

EA\ - разрешение обращения во внутреннюю память программ;

T0,T1 - входы счетчиков внешних событий;

INT0,INT1- запросы внешних радиальных прерываний;

RxD - вход данных последовательного канала;

TxD - выход данных последовательного канала.

В состав МК51 входят параллельные 8-разрядные квазидвунаправленные порты P0..P3. Порт Р3 может быть использован для ввода и вывода управляющих сигналов.

Таким образом, в циклах обращения к внешним ресурсам на линиях порта P3 работают управляющие сигналы, а при отсутствии необходимости управления внешними ресурсами эти же линии могут быть использованы как линии порта.

Архитектурные особенности МК51

МК51 позволяет управлять пятью (частично пересекающимися) адресными пространствами памяти, четыре из которых являюся областями данных:

RSEG - пространство регистров (4*8 байт);

DSEG - пространство внутренней памяти данных (256 байт);

BSEG - битовое пространство данных (256 бит);

XSEG - пространство внешней памяти данных (до 64К байт);

CSEG - пространство программного кода (до 64К байт).

Пространства RSEG и BSEG частично пересекаются, физически совмещаются с DSEG и образуют единую внутреннюю среду для хранения данных. Это позволяет одни и те же данные рассматривать с разных позиций (ячейка памяти, регистр, битовое поле, порт ввода/вывода и т.п.) и организовывать наиболее удобный для данного случая доступ к ним.

Характерно, что все порты ввода/вывода, системные регистры, таймеры так же отображены на пространство DSEG.

Пространство регистров представлено четырьмя банками регистров по 8 в каждом, а так же 16-разрядными программным счетчиком PC и регистром косвенного адреса DPTR, 8-разрядными аккумуляторами A и B, указателем стека SP и регистром PSW.

Все регистры, кроме PC, отображаются на DSEG.

PSW[7] - CY - перенос из старшего (7) разряда АЛБ;

PSW[6] - AC - перенос из третьего разряда АЛБ;

PSW[5] - F0 - флаг пользователя.

Кроме того, формат PSW включает двухбитовое поле PSW[4:3] - RS номера банка регистров и флаги арифметического переполнения OV (PSW[2]) и четности P (PSW[0]).

Флаги CY, AC и OV отражают признаки результата последней арифметической операции, а P - четность содержимого аккумулятора A. Расширение аккумулятора B используется в командах умножения и деления, а в остальных операциях - как обычная ячейка памяти. Программный счетчик адресует пространство памяти программ CSEG объемом до 64K байт, причем переход из области внутренней памяти программ к внешней осуществляется автоматически.

Указатель данных DPTR используется для обращения к XSEG и при пересылке констант из CSEG в A. Кроме того, содержимое DPTR используется а качестве смещения в команде перехода.

Указатель стека SP образует системный стек глубиной до 256 байт. SP хранит адрес последнего занесенного байта и растет при записи в сторону больших адресов.

Регистры R0, R1 каждого банка используются в качестве указателей данных. При сбросе машины в A, B, PC и DPTR загружаюся 0h, а в SP - 07h.