Цифро-аналоговые и аналого-цифровые преобразователи

Цифро-аналоговые преобразователи (ЦАП) и аналого-цифровые (АЦП) применяются в информационно-измерительных системах, в технике связи, в цифровом телевидении, в бытовой технике и т. п.

ЦАП с весовыми резисторами

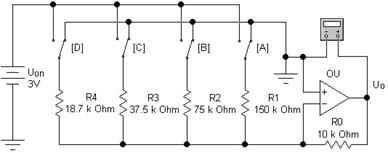

Цифро-аналоговые преобразователи используются для преобразования цифрового кода в аналоговый сигнал. ЦАП с весовыми резисторами (рис. 6.1) состоит из двух уз лов: резистивной схемы (матрицы) на резисторах R1...R4 и суммирующего усилителя (ОУ OU с резистором обратной связи Ro) Опорное напряжение Uon (3 В) подключается к резисторам матрицы переключателями D, С, В и А, имитирующими преобразуемый код. Выходное напряжение Uo измеряется мультиметром. Такой ЦАП относится к устройствам прямого преобразования.

Рис. 6.1. ЦАП с весовыми резисторами

Если все переключатели замкнуты на «землю», как показано на рис. 6.1 напряжение выходе ОУ равно 0 В. Допустим, что переключатель А установлен в положение, логической 1. Тогда на вход 01 через резистор R1 подается напряжение 3 В. Рассчитаем коэффициент усиления напряжения: К = Ro/R1 = = 10000/150000 = 0,066. Выходное напряжение ОУ Uo = 0,066·3 = 0,2 В. При подаче двоичной комбинации 0001 на входе, на выходе ОУ напряжение 0.2 В.

Точность такого преобразователя определяется разбросом и стабильностью параметров резисторов матрицы, аналоговых ключей, ОУ.

ЦАП лестничного типа

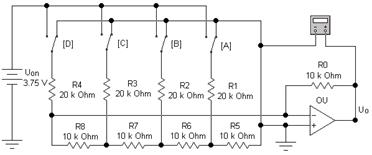

Схема ЦАП такого типа (рис. 6.2) состоит из резистивной матрицы

R – 2R, напоминающей лестницу, и суммирующего усилителя. Сопротивление каждого из резисторов R1...R5 равно 20 кОм, а резисторов R6...R8,

Ro – 10 кОм. Отметим, что сопротивления горизонтально расположенных резисторов «лестницы» ровно в 2 раза больше сопротивлений вертикальных.

Рис. 6.2. ЦАП с лестничного типа

Переход к каждой следующей двоичной последовательности приводит к увеличению аналогового сигнала на 0,25 В. Опорное напряжение выбрано равным 3,75 В из соображения удобства сопряжения с ИМС семейства ТТЛ при замене ключей A...D такими ИМС.

Выходное напряжение ЦАП на рис. 6.2 определяется по формуле:

Uo = UonRo[К12n-1 + К22n-2+ ... + К i2n - i+ К n]/R2n, (1)

где Кi – значение цифрового сигнала (0 или 1) на i-м входе, n – число разрядов преобразования (для схемы на рис. 6.2 n = 4), R – сопротивление резистора матрицы R – 2R (R = 10 кОм для схемы).

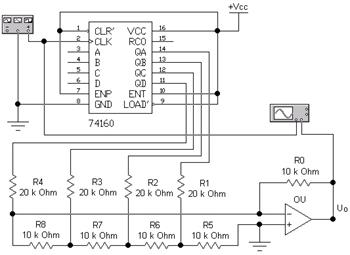

На рис 6.3 показана схема ЦАП с использованием коммутирующего устройства двоично-десятичного счетчика 74160 (К155ИЕ9)

Рис.6.3. Четырехразрядный ЦАП лестничного типа на базе счетчика 74160

|

|

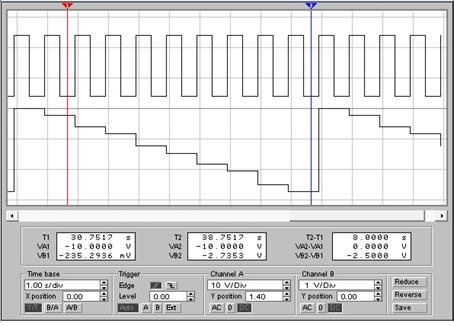

Рис.6.4. Осциллограммы сигналов на его счетном входе (A)

и выходе ЦАП (B) схемы рис. 6.3

Параллельные АЦП

Большинство высокоскоростных осциллографов и некоторые высокочастотные измерительные приборы используют параллельные АЦП из-за их высокой скорости преобразования, которая может достигать 5Г (5*109) отсчетов/сек для стандартных устройств и 20Г отсчетов/сек для оригинальных разработок. Обычно параллельные АЦП имеют разрешение до 8 разрядов, но встречаются также 10-ти разрядные версии.

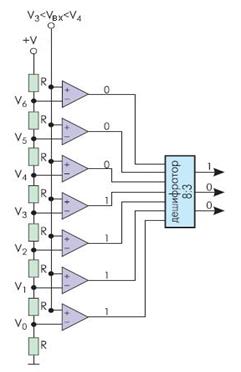

На рис. 6.5 показана упрощенная блок-схема 3-х разрядного параллельного АЦП. Здесь используется массив компараторов, каждый из которых сравнивает входное напряжение с индивидуальным опорным напряжением. Такое опорное напряжение для каждого компаратора формируется на встроенном прецизионном резистивном делителе. Значения опорных напряжений начинаются со значения, равного половине младшего значащего разряда, и увеличиваются при переходе к каждому следующему компаратору с шагом, равным V/23. В результате для 3-х разрядного АЦП требуется 23 – 1 или семь компараторов. А, например, для 8-разрядного параллельного АЦП потребуется уже 255 (или (28 – 1)) компараторов.

Рис 6.5. Блок-схема 3-х разрядного параллельного АЦП

С увеличением входного напряжения компараторы последовательно устанавливают свои выходы в логическую единицу вместо логического нуля, начиная с компаратора, отвечающего за младший значащий разряд. Между V3 и V4, таким образом, 4 нижних компаратора имеют на выходе «1», а верхние три компаратора – «0». Дешифратор преобразует (23 – 1) – разрядное цифровое слово с выходов компараторов в двоичный 3-х разрядный код.

Параллельные АЦП – достаточно быстрые устройства, но они имеют свои недостатки. Из-за необходимости использовать большое количество компараторов параллельные АЦП потребляют значительную мощность,