Мультиплексором называется комбинационная схема, имеющая m + 2m входов и один выход, где m – число адресных входов, а 2m – число информационных входов.

Таблица 2.4

| А | x0 | x1 |  y y

|

| 0 | 0 1 | * | 0 1 |

| 1 | * | 0 1 | 0 1 |

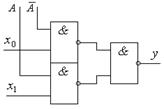

Рис. 2.5

Основное назначение мультиплексоров состоит в коммутации на один выходной канал информации, поступающей по нескольким входным каналам.

В простейшем мультиплексоре-селекторе «две линии к одной» (2:1) с одним адресным входом A (рис. 2.5) при A = 0, y = x0, а при A = 1, y = x1 (табл. 2.4), чему соответствует логическое уравнение

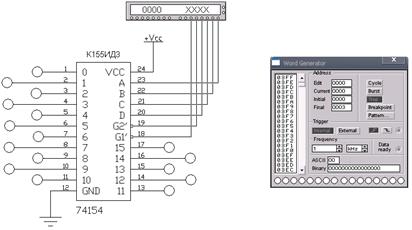

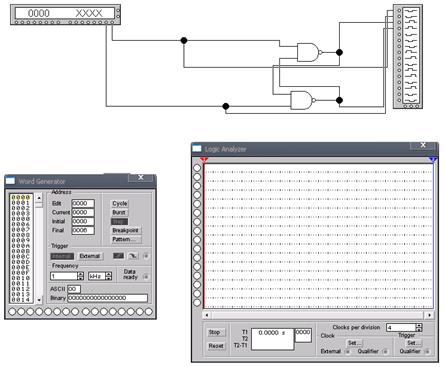

На рис. 2.6 приведена схема включения дешифратора (дешифратор

4´16) 74154 (К155ИД3): входы А, В, С, D – адресные; выходы 0…15 – инверсные; входы G1, G2 – разрешения. В режиме дешифратора с генератора слова на входы G1, G2 подается 0, а на адресные входы – код в диапазоне 0000….1111. В режиме демультиплексора один из разрешающих входов, например G1, используется в качестве информационного.

Рис. 2.6. Дешифратор схема включения ИМС 74154 (К155ИД3)

Компараторы. Компаратором называется цифровое устройство сравнения кодов чисел. В общем случае компаратор параллельных кодов двух m-разрядных двоичных чисел представляет собой комбинаторную схему с 2m входами и тремя выходами (равно, больше, меньше). При поступлении на входы кодов сравниваемых чисел сигнал логической единицы появляется только на одном из выходов.

Таблица истинности (табл. 2.5) компаратора двух одноразрядных чисел x1 и x2 приводит к логическим функциям:

Таблица 2.5

| x1 | x2 | y= | y> | y< | |

| 0 | 0 | 1 | 0 | 0 | |

| 0 | 1 | 0 | 0 | 1 | |

| 1 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 1 | 0 | 0 |

|

Синтезированная в базисе И-НЕ по этим уравнениям схема компаратора имеет вид (рис. 2.7):

Рис. 2.7

Основные области применения компараторов: выделение числа в потоке цифровой информации, формирование условных переходов при реализации микропрограмм, контроль и диагностика узлов ЭВМ.

ЛАБОРАТОРНОЕ ЗАДАНИЕ

1. Проверить правильность функционирования дешифратора, собранного по схеме 2.1а с использованием логического преобразователя и генератора слова. Для индикации состояний входов и выходов используйте светоиндикаторы логических уровней.

2. Проверить правильность функционирования шифратора, выполненного по схеме 2.3 с использованием логического преобразователя и генератора слова. Для индикации состояний входов и выходов используйте светоиндикаторы логических уровней.

3. Взяв за основу схему 2.4, построить демультиплексор 1:4 в базисе

И-НЕ и проверить правильность его функционирования с использованием логического преобразователя и генератора слова. Для индикации состояний входов и выходов используйте светоиндикаторы логических уровней.

4. Взяв за основу схему 2.5, построить мультиплексор 2:1 для коммутации двухразрядных входных сигналов x0 и x1 с использованием логического преобразователя и генератора слова. Для индикации состояний входов и выходов используйте светоиндикаторы логических уровней.

5. Оценить экспериментально правильность функционирования компаратора, представленного на рис. 2.7 с использованием логического преобразователя и генератора слова. Для индикации состояний входов и выходов используйте светоиндикаторы логических уровней.

6. Подготовьте выходные кодовые комбинации генератора слова в схеме на рис. 2.6 обеспечивающие поочередное включение светоиндикаторов на выходе дешифратора, начиная с выхода 0.

7. Переведите дешифратор в схеме на рис. 2.6 в режим демультиплексор и выполните задание в объеме п. 6.

Содержание отчета

Наименование и цель работы; краткие сведения из теории; результаты проведенных исследований схем, которые должны быть приведены в отчете вместе с описанием их работы; разработанные согласно задания схемы и кодовые комбинации генератора слова; выводы по работе.

Контрольные вопросы

1 При решении, каких задач цифровой техники используются дешифраторы?

2 Что собой представляет шифратор, при решении каких задач он используется?

3 Что собой представляет мультиплексор, каково его назначение?

4 Что такое демультиплексор, для решения каких задач его можно применить?

5 На объекте управления, связанном с удаленной управляющей ЭВМ двухпроводной линией связи, расположены 8 датчиков и такое же количество исполнительных устройств (электродвигателей, электромагнитов и т. п.). Где в такой системе управления необходимо поставить мультиплексор и демультиплексор? Каковы требования к форме сигналов датчиков и исполнительных устройств?

Литература [3], [6], [1], [5].

Лабораторная работа № 3

ТРИГГЕРЫ

Цель работы: изучение принципов построения и алгоритмов функционирования различных триггерных схем на логических элементах и в виде специализированных ИМС серии К155.

ОБЩИЕ СВЕДЕНИЯ

Триггеры – устройства последовательного типа, обладающие памятью и служащие для хранения одного бита информации.

Триггеры имеют два устойчивых состояния (0 и 1), определяемых по уровню напряжения на его прямом выходе. Состояние триггера изменяется скачкообразно под действием входных сигналов.

Основой для построения триггеров служат логические элементы потенциального типа. Триггеры находят широкое применение в качестве цифровых устройств, реализующих определенные логические функции. На базе триггеров выполняется целый ряд цифровых устройств – регистры, счетчики, запоминающие устройства и др.

Триггеры классифицируют по назначению (виду логического уравнения, связывающего переменные на входах и выходе до и после перехода триггера из одного состояния в другое) и способу функционирования во времени.

RS -триггеры. RS-триггер имеет два информационных входа R и S и функционирует в соответствии со следующей таблицей переходов состояний (табл. 3.1).

Таблица 3.1

| Такт n | Такт n+1 | Операция | ||

| Rn | Sn | Qn | Qn +1 | |

| 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 0 0 0 0 1 1 1 1 | 0 1 0 н/о 1 1 0 н/о | хранение 0 запись 1 запись 0 не определенное состояние хранение 1 запись 1 запись 0 не определенное состояние |

Вход S (set – установка) служит для установки триггера в единичное состояние, вход R (reset – сброс) – для установки в нулевое состояние.

Комбинация сигналов Rn = Sn = 1 вызывает неопределенное состояние на выходе триггера и является запрещенной.

Как следует из табл. 3.1, логическое управление асинхронного RS-триггера имеет вид

.

.

В базисах И–НЕ, И–ИЛИ–НЕ это уравнение примет вид

,

,

.

.

|

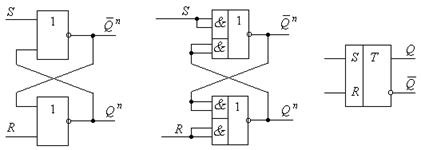

Схемы асинхронных триггеров, соответствующие полученным уравнениям, и их условные обозначения приведены на рис. 3.1 и 3.2.

|

Рис. 3.1

Рис. 3.2

Минимизированная таблица переходов состояний, приведенных триггеров имеет вид (табл. 3.2)

Таблица 3.2

| Rn | Sn | Qn+1 |

|

| Qn+1 |

| 0 | 0 | Qn | 0 | 0 | н/о |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | н/о | 1 | 1 | Qn |

-триггер, показанный на рис. 3.1, с инверсным управлением, RS-триггер на рис. 3.2 с прямым управлением.

-триггер, показанный на рис. 3.1, с инверсным управлением, RS-триггер на рис. 3.2 с прямым управлением.

На рис 3.3 показана схема в программе EWB асинхронного RS-триггера на ЛЭ И–НЕ с использованием информационных входов заданных генератором слова и выходов показанных на логическом анализаторе

Рис. 3.3. Схема в программе EWB асинхронного RS-триггера

В синхронных RS-триггерах на входе каждого плеча имеется схема совпадения, поэтому информация на входы соответственно триггеров поступает только при наличии тактирующих сигналов, поступающих на вход C.

Синхронный триггер при С = 0 не изменяет предыдущего состояния, а при С = 1 функционирует как асинхронный. Схема синхронного RS-триггера в базисе И–НЕ и его временная диаграмма приведены на рис. 3.4.

|

Рис. 3.4

D -триггеры. Синхронные D-триггеры подчиняются следующему логическому уравнению:

.

.

При С = 0 сохраняется предыдущее состояние  , а при С = 1,

, а при С = 1,  , т. е. на выходе триггера, в такте n +1 появится тот же сигнал, который был на его входе D в такте n. Таким образом, D-триггер осуществляет задержку входного сигнала на один такт.

, т. е. на выходе триггера, в такте n +1 появится тот же сигнал, который был на его входе D в такте n. Таким образом, D-триггер осуществляет задержку входного сигнала на один такт.

В серии ИМС К155 D-триггеры представлены достаточно широко. Наибольший интерес представляет собой микросхема К155ТМ2 (в программе EWB аналог 7474), содержащая два D-триггера с прямым динамическим тактированием (по изменению уровня тактирующих импульсов от 0 к 1) и дополнительными инверсными входами R и S для асинхронной установки триггера в 0 и 1.

Условия обеспечения различных режимов работы триггера К155ТМ2 приведены в табл. 3.3, а его условное графическое обозначение на рис. 4.4:

Таблица 3.3

| Режим | R | S | C | D | Qn+1 | |

| Асинхронный | 0 | 1 | * | * | 0 | |

| 1 | 0 | * | * | 1 | ||

| 0 | 0 | * | * | н/о | ||

| Синхронный | 1 | 1 | 0 | 0 | ||

| 1 | 1 | 1 | 1 | |||

| Хранение | 1 | 1 | * | Qn | ||

| 1 | 1 | 1 | * | Qn | ||

| 1 | 1 | 0 | * | Qn | ||

Символом * в таблице 3.3 обозначены сигналы, не имеющие значения для данного режима.

Т-триггеры. Т-триггер – это счетный триггер с одним информационным входом Т, изменяющий свое состояние на противоположное с приходом каждого счетного сигнала (табл. 3.4). Так как счетные триггеры со статическим управлением не используются, счетным сигналом являются перепады напряжения 0 ® 1 или 1® 0. На практике Т-триггеры выполняют на основе других типов триггеров, например D-триггеров (рис. 3.6).

Таблица 3.4

| T | Qn+1 | | Qn+1 | ||||||

| 0 | Qn | 0 | Qn | ||||||

| 1 | Qn | 1 | Qn | ||||||

|

| Qn | ||||||||

| Qn |

| ||||||||

|

Рис. 3.6 Рис. 3.7

Как следует из рис. 3.7, Т-триггер является делителем частоты следования счетных импульсов в два раза.

JK -триггеры. JK-триггер имеет два информационных входа J и K, причем при J = K = 1 триггер инвертирует предыдущее состояние, а при остальных комбинациях сигналов на входах функционирует как RS-триггер, если принять J-вход за S-вход, а вход K – за вход R (табл. 3.5).

Логическое уравнение асинхронного JK-триггера имеет вид

Логическое уравнение асинхронного JK-триггера имеет вид

.

.

На практике применяются исключительно синхронные JK-триггеры. Для повышения стабильности работы эти триггеры выполняются с двухступенчатым управлением, где обе ступени тактируются с разделением во времени. К таким триггерам относятся ИМС К155ТВ1. Тактирование первой ступени осуществляется перепадом напряжения 0 → 1, второй – перепадом 1 → 0. Данный триггер, подобно триггеру К155ТМ2, имеет асинхронный режим с управлением по входам  .

.

Еще одной особенностью этого триггера является наличие 3-х входов J и 3-х входов K, которые соответственно объединены логическими схемами ЗИ на входах триггера.

На базе JK-триггера может быть выполнен широкий набор триггеров других типов, в связи с чем JK-триггеры считаются универсальными (рис. 3.8, 3.9).

|

Рис. 3.8 Рис. 3.9

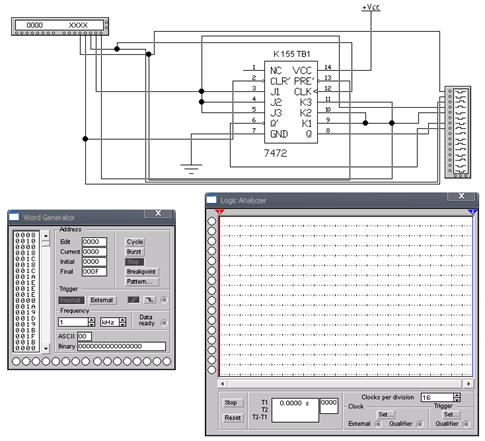

Схема JK-триггера К155ТВ1 аналог в программе EWB 7472 – показан на рис. 3.10, где обозначено: J, K – информационные входы; > – тактовый вход; вывод сверху – асинхронная предустановка триггера в единичное состояние (Q = 1) вне зависимости от состояния сигналов на входах (функционально аналогичен входу S RS-триггера); вывод внизу – асинхронная предустановка в нулевое состояние (так называемая очистка триггера, после которой Q' = 1); наличие кружочков на изображениях выводов обозначает, что активными являются сигналы низкого уровня, а для тактового входа – что переключение триггера производится не по переднему фронту тактового импульса, а по его срезу (по заднему фронту импульса). Входы поданы с генератора слова, выходы можно посмотреть на логическом анализаторе.

Рис. 3.10. Схема К 155 ТВ1 (7472)

ЛАБОРАТОРНОЕ ЗАДАНИЕ

1. Собрать схемы асинхронного RS-триггера (по аналогии рис. 3.3) на ЛЭ И-НЕ и ИЛИ-НЕ (рис. 3.1 и 3.2), исследовать их работу в статическом режиме (табл. 3.2).

2. Подав на входы R и S сдвинутые во времени серии импульсов с генератора слова и пользуясь логическим анализатором, получить временные диаграммы работы триггеров. Обеспечить при этом отсутствие запрещенных комбинаций входных сигналов.

3. Исследовать работу синхронного RS-триггера (рис. 3.4) в статическом режиме применив схему по аналогии рис. 3.3.

4. Исследовать работу одного из триггеров ИМС К155ТМ2(7474) в асинхронном и синхронном режимах (табл. 3.4). Входные сигналы подать с генератора слова, выход посмотреть на логическом анализаторе. При помощи визирных линеек показать работу триггера в зависимости от входных сигналов.

При испытании ИМС D-триггера 7474 (155ТМ2), выводы которой имеют следующие назначения (для необозначенных в тексте раздела): CLR', PRE' – R- и S-входы (инверсные);

CLK – тактовый вход.

5. Испытать работу D-триггера (К155ТМ2 (7474)) в режиме T-триггера. Построить временную диаграмму его работы. Входные сигналы подать с генератора слова, выход посмотреть на логическом анализаторе. При помощи визирных линеек показать работу триггера в зависимости от входных сигналов.

6. Исследовать работу JK-триггера (К155ТВ1 (7472)) в синхронном режиме (табл. 3.5). Входные сигналы подать с генератора слова, выход посмотреть на логическом анализаторе. При помощи визирных линеек показать работу триггера в зависимости от входных сигналов .

7. Испытать работу JK-триггера в режимах D- и T-триггеров. Построить временные диаграммы. Входные сигналы подать с генератора слова, выход посмотреть на логическом анализаторе. При помощи визирных линеек показать работу триггера в зависимости от входных сигналов .

Содержание отчета

1. Таблицы переходов состояний, логические уравнения и схемы исследуемых в работе триггеров.

2. Совмещенные во времени осциллограммы напряжений по п. 2.

3. Построенные временные диаграммы по п. 4, 7.

4. Выводы по работе.

Контрольные вопросы

1. Почему триггеры относят к последовательным устройствам?

2. Какие типы триггеров Вы знаете, чем обусловлено их многообразие?

3. Как работает асинхронный триггер?

4. Как работает синхронный триггер?

5. Как работает двухступенчатый триггер?

6. Что такое статическое и динамическое управление записью?

7. Какие входные сигналы различают у триггеров?

8. Как подразделяются входы триггеров?

Литература: [3, 5, 4]

Лабораторная работа № 4

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ ЦИФРОВЫЕ УСТРОЙСТВА

Цель работы: изучение принципов построения и функционирования цифровых счетчиков и регистров на базе триггеров ИМС серии К155 и их экспериментальное исследование.

ОБЩИЕ СВЕДЕНИЯ

Счетчиком называется цифровое устройство, предназначенное для подсчета количества входных импульсов, а также формирования и запоминания двоичного кода числа, соответствующего этому количеству.

По порядку изменения состояния счетчики бывают с естественным порядком счета, когда значение кода каждого последующего состояния отличается на единицу от кода предыдущего состояния, и с произвольным порядком счета, когда значения кодов соседних состояний отличаются больше чем на единицу.