3. Анализ существующих программируемых логических интегральных схем

ИССЛЕДОВАТЕЛЬСКАЯ ЧАСТЬ

1.Анализ технического задания

2.ПАТЕНТНО-ИНФОРМАЦИОННЫЙ АНАЛИЗ

Разработка шифрования аппаратными средствами , в каждом случае обуславливается созданием уникального устройства криптографической защиты и передачи данных. Оно не имеет прототипов или аналогов. Однако существуют схожие системы связи, оповещения и передачи цифровой информации. Эти устройства имеют в своем составе подсистемы обеспечивающие криптографическую защиту передаваемой информации. Однако большая часть таких устройств в которых КЗИ реализована по ГОСТ 28147-89 являются «закрытыми» .Т.е приводить как пример их названия и ТТХ незаконно, и влечет ответственность за нарушение гос. тайны.

Все же есть и открытые изделия в составе имеющие наиболее схожую КЗИ с разрабатываемой , их названия, описание применения , а так же ТТХ приведены ниже.

2.1 Изделие Е-61РА

2.1.1 Изделие Е-61РА обеспечивает:

· передачу данных со встроенными средствами криптографической защиты при использовании совместно с ЭВМ, имеющей выходной последовательный интерфейс типа RS-232 (RS-422), осуществляет функции изделия передачи данных с использованием шифрования и имитозащиты информации в реальном масштабе времени;

· установку с отображением на табло, запись и хранение при пропадании питания в "записной книжке" 16 двадцатизначных номеров абонента, включая программируемую паузу, заданных режимов работы, времени, даты и дня недели;

· следующие алгоритмы передачи данных в реальном масштабе времени:

o алгоритмы режимов «СС-ПС-1» и «СС-ПС-2» с четырьмя подрежимами (с адресом и без адреса) с засекречиванием и без засекречивания, с контролем передачи и без контроля передачи;

o алгоритм режима «СС-ПД» – передача данных в режиме «Дуплекс-2», с обратной связью и несколькими градациями;

o алгоритм режима « СС-С» – для скоростей от 1200 до 16000 бит/с;

· обмен информацией по интерфейсам:

o С1-ФЛ (С1-И) со скоростями передачи 1200, 2400, 4800, 9600, 16000 бит/c;

o И-РС со скоростями передачи 1200, 2400, 4800, 9600, 16000 бит/c;

o С1-ТЧ со скоростями передачи 600 и 1200 бит/c (частотная модуляция); 1200, 2400 и 4800 бит/c (фазовая модуляция) при наличии модемного модуля ВТ01-414.2 (2 и/или 4 канал);

o С1-ТГ со скоростями передачи 50, 75, 100, 200, 300 бит/c (симметричный сигнал); 300, 600, 1200, 2400, 4800 бит/c (асимметричный сигнал) при наличии модуля ВТ01 414.4 (2 и/или 4 канал);

o RS-232 со скоростями передачи 600, 1200, 2400, 4800, 9600 бит/c;

o RS-422 со скоростями передачи 600, 1200, 2400, 4800, 9600 бит/c;

o ОЦК со скоростью передачи 64000 бит/с при наличии модуля ВТ01 414.7 (2 и/или 4 канала);

· программное переключение типов стыков для каждого канального выхода. Типы стыков задаются программным путем или внешней ответной частью соединителя, подключаемого к канальному выходу изделия;

· передачу (прием) информации по предварительно скоммутированному каналу связи через внешнее устройство (модем), подключаемое по стыку RS-232 со скоростями 1200, 2400, 4800, 9600, 19200 бит/с;

· ввод ключевой документации в изделие осуществляется с внешнего устройства ввода ключевой документации UVK F 240;

· работу по четырем независимым каналам;

· имеет встроенный функциональный контроль, обеспечивающий проверку исправности при включении и в процессе работы изделия;

· электропитание – от сети постоянного тока напряжением от 11 до 36 В;

· потребляемая мощность – не более 25 Вт;

· габаритные размеры – 335х300х36 мм;

· масса изделия – не более 4 кг.

2.2 Аппаратура криптографической защиты документальной информации. Т-237Е

Предназначена для криптографической защиты, имитозащиты, помехоустойчивой передачи (приема) данных, их распределения между каналами связи и автоматизированными рабочими местами:

2.2.1 Аппаратура обеспечивает:

· полную автоматизацию процессов приема, обработки и распределения сообщений четырех категорий срочности в симплексном, полудуплексном и дуплексном режимах;

· автоматическую криптографическую защиту;

· автоматический выбор маршрута доведения сообщения до адресата;

· защиту от тиражирования пакетов в сети и навязывания ранее переданных;

· режим упорядоченной (с анализом занятости канала или без анализа занятости канала) передачи данных в радио- и проводных сетях связи;

· количество обслуживаемых каналов связи - 2 или 4;

· типы стыков с каналообразуюшей аппаратурой и скорость передачи по каналам:

| С1-ТЧ | 1,2 Кбит/с |

| С1-ФЛ-БИ с двухпроводной схемой подключения | 1,2; 2,4; 4,8; 9,6; 16; 32; 48; 64 Кбит/с |

| С1-ФЛ-БИ для сопряженной работы с радиостанциями, с симметричной четырехпроводной схемой подключения | 1,2; 2,4; 4,8; 9,6; 16; 32 Кбит/с |

| С1-ТГ с симметричной четырехпроводной схемой подключения | 50; 75; 100; 150; 200; 300; 500 бит/с |

| С1-ТГ с несимметричной четырехпроводной схемой подключения | 50; 75; 100; 150; 200; 300; 500; 1200; 2400; 4800; 9600; 16000; 32000 бит/с |

| ОЦК | 64 Кбит/с |

| С1-И-РС | 16; 32 Кбит/с |

| типы стыков с ООД | мультиплексный (основной и резервный) RS-232 |

| носитель ключевой информации | перфолента |

2.2.2Назначение составных устройств аппаратуры:

UVK-F-240 - устройство ввода ключевой информации с перфоленты.

Коробка распределительная GА011 - для организации многоточечной проводной сети связи (подключаются до десяти двухпроводных линий связи). Для увеличения числа абонентов до 20 параллельно подключаются две коробки. При этом допускается взаимное удаление абонентов сети при скорости передачи 16 Кбит/с до 5 км, а при скорости 1,2 Кбит/с - до 15 км.

2.3 Аппаратура автоматического засекречивания речевой информации Е-58 с обеспечением режима "Абонент - секретарь"

2.3.1 "Абонент - секретарь" предназначена :

для организации в режиме "Абонент-Секретарь" защищенного обмена речевой информации между абонентами сети ТфОП с 2-х или 4-х проводным окончаниями на скоростях 2,4; 4,8; 9;6 кбит/с и обеспечивает:

· Ведение открытых и защищенных речевых переговоров;

· Отображение на табло открытого или закрытого режимов работы, номера вызываемого абонента и продолжительности разговора по его окончании, аутентификационных признаков встречноработающего абонента;

· Сохранение в памяти последнего набранного номера и его автоматический дозвон;

· набор, хранение в памяти "записной книжки" 16-х номеров до 24-х знаков каждый и ускоренный набор хранимых номеров;

· При пропадании электропитания сети переменного тока хранение информации:

o об установленных режимах

o о времени, дате, дне недели

o о номерах "записной книжки*

o об аварии аппаратуры

o о факте НДC.

2.3.2 Состав аппаратуры:

Аппарат секретаря - обеспечивает возможность ведения открытых и защищенных речевых переговоров.

Выносной телефонный аппарат обеспечивает возможность ведения открытых и защищенных речевых переговоров через аппарат секретаря.

3.АНАЛИЗ СУЩЕСТВУЮЩИХ ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ

Главным составляющим элементом разрабатываемой СКЗИ , является ПЛИС. Для того чтобы оптимизировать работу конфигурируемых схем , необходимо провести анализ архитектуры, структуры логических базовых элементов и других технических характеристик .Так же выбрать необходимый компилятор с удобным интерфейсом ,и со всеми необходимыми функциями для настройки и отладки разрабатываемого проекта.

Исходя из этого мною был проведен анализ ПЛИС(FGPA) по основным пунктам.

3.1 Архитектура программируемых логических интегральных схем (ПЛИС или FPGA)

FPGA – это аббревиатура с английского Field Programmable Gate Array.

документациях и описаниях вместо слова FPGA.

ПЛИС и FPGA –Это микросхемы, которые применяются для разработки индивидуальной структуры цифровых интегральных схем.

Логика работы ПЛИС задается не изготовителем микросхемы, а с помощью программирования в специальных и программных обеспечениях и программаторов.

Микросхемы ПЛИС – не являются микропроцессорами, в которых пользовательские задачи выполняется последовательно, команда за командой. В ПЛИС специально разрабатывается нужная программисту схема для определенной задачи, состоящая из триггеров и логики.

Проект для ПЛИС как один из вариантов может быть разработан в виде принципиальной схемы. Так же имеются специальные языки программирования VHDL или Verilog. Текстовое и графическое описание проекта выводит цифровую электронную схему, которая в в конце концов будет «вшита» в ПЛИС.

Микросхема ПЛИС ,обычно , состоит из:

· конфигурируемых логических блоков, реализующих требуемую логическую функцию;

· программируемых электронных связей между конфигурируемыми логическими блоками;

· программируемых блоков ввода/вывода, обеспечивающих связь внешнего вывода микросхемы с внутренней логикой.

Но в современных ПЛИС часто встраивают дополнительно блоки DSP, PLL, блоки памяти или умножители и другие компоненты.

Разработчик проекта ПЛИС задает желаемую логику работы своей уникальной будещей микросхемы в виде блочной схемы или програмного текста на VHDL/Verilog. Компилятор же , распознавая внутреннее устройство FPGA пытается разместить полученную схему по имеющимся логическим конфигурируемым блокам и старается объеденить эти блоки с помощью имеющихся разрабатываемых электронных связей . Трассировка и размещение связей между логическими блоками в ПЛИС производит компилятор.

3.2 Классификация по типу хранения конфигурации ПЛИС.

SRAM-Based - является одной из самых распространенных разновидностей ПЛИС. Конфигурация ПЛИС находится в ячейках постоянной памяти, изготовленной по стандартной технологии CMOS (CMOS, complementary metal-oxide-semiconductor ,комплементарная структура металл-оксид-полупроводник ).

Плюс данной технологии – возможность неоднократного перепрограммирования ПЛИС.

Недостатки – обладает не высоким быстродействием, после подачи питания нужно вновь загружать прошивку. Из этого следует что на плате необходо установить дополнительно специальную микросхему FLASH , загрузчик, или микроконтроллер – все это повышает цену конечного устройста и понижает процент отказоустойчивости .

Flash-based - В этих микросхемах хранение изменений происходит в памяти типа EEPROM или во внутренней памяти FLASH. Данные ПЛИС выделяются тем , что при подаче питания запрограммированная прошивка не стирается. После включения питания ПЛИС снова готова к работе. Но, у этого типа микросхем имеются и недостатки. Исполнение FLASH памяти внутри микросхемы CMOS – не является простой задачей. Для этого необходимо совместить два совершенно разных нано-техпроцесса для выпуска данных микросхем. Следовательно цена за такие ПЛИС увличивается. По мимо всего прочего , такие микросхемы, как показывает практика, обладают ограниченным количеством циклов перезаписи.

Antifuse – это специальная технология, по которой выполняются ПЛИС программируемые однократно. Программирование этих ПЛИС заключается в расплавлении в определенных местах чипа специальных перемычек для образования микросхемы с нужной конфигурацией.

Минус заключается в том , что прошивать / программировать ПЛИС возможно только однократно. После программирования, если в прошивке были недочеты или ошибки их исправить уже невозможноя. Так же процесс прошивки не быстрый, однако множество достоинств у данных ПЛИС: они быстрые (имеют возможность работы на больших частотах), имеют хорошую стойкость при воздействии радиации – все благодаря тому , что конфигурация выходит в виде перемычек, а не в виде дополнительной логики, как у типа SRAM-based.

3.3 Конфигурируемые логические блоки.

В документации, известного производителя ПЛИС, компании Альтера можно наткнуться на выражение Logic Array Block (LAB) – массив логики. У компании Xilinx в чипах ПЛИС имеются примерно похожие блоки - Configurable Logic Block (CLB). Конфигурируемый логический блок – это основной элемент в ПЛИС, в котором может быть произведена какая-либо простая логическая функция или исполнено хранение полученного значения вычисления в триггерах (регистрах).

Трудоемкость и структура создаваемого логического блока (CLB) определяет производитель.

В теории , конфигурируемый логический блок может являться, как пример, совершенно простым, как отдельный транзистор. Или же он может быть сложным, представляя из себя целый процессор - это крайние точки исполнения.

В первом варианте необходимо огромное количество программируемых связей, для того чтобы затем из раздельных транзисторов объединить нужную схему. Во другом случае связей может быть нужно не так много, но пропадает гибкость проектирования логической схемы.

Следуя из этого конфигурируемый блок представляет из себя что-то среднее: он достаточно сложен, чтобы возможно было запрограммировать туда определенную функцию, но и имеет довольно малые размеры, чтобы разместить большое количество таких блоков в самой ПЛИС и чтобы была возможность объединить их в единую схему.

Исходя из всего вышесказанного , выбор структуры конфигурируемого логического блока компанией производителем ПЛИС – это каждый раз поиск консенсуса по быстродействию, по площади кристалла, потреблению энергии и так далее.

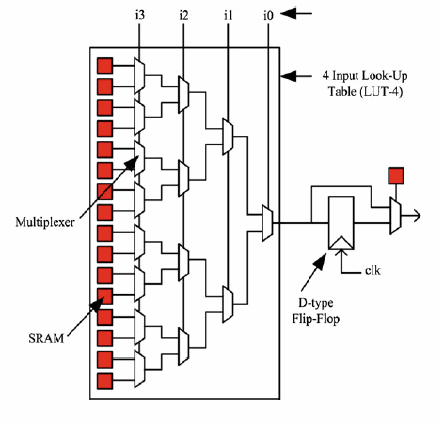

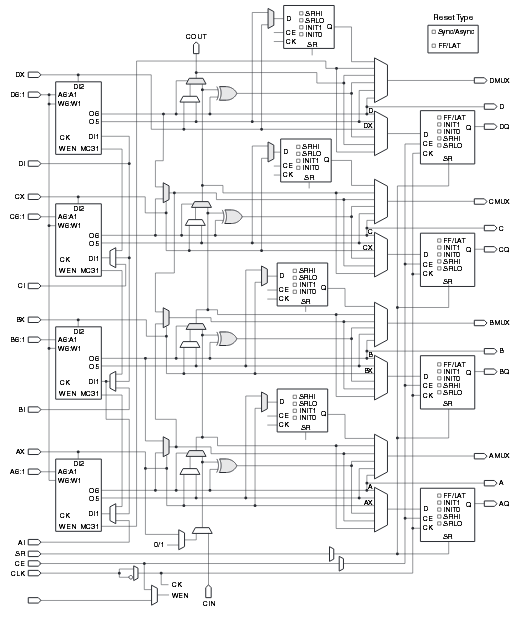

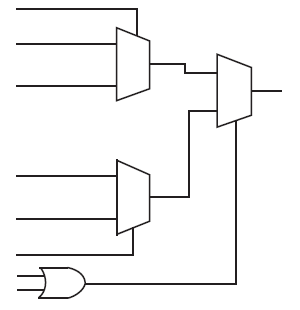

Конфигурируемый логический блок может иметь структуру из одного или нескольких базовых логических элементов. В англоязычной документации - Basic Logic Element (BLE) или Logic Element (LE). В ПЛИС по умолчанию применяются так называемые LUT-based логические базовые элементы. (Рис1)

Рис. 1. Пример базового логического элемента.

LUT (Look-Up Table),это таблица преобразования.На Рис.1 изображён четырехбитный LUT в связи с базовым логическим блоком. Здесь числу в четыре бита на входе логической функции устанавливается в соответствие однобитный число. Красные квадраты на обозначают собой программируемый элемент, регистр – это та память, где сохраняется прошивка для ПЛИС. Можно увидеть, что для получения 4-х битного LUT необходимо 16 конфигурационных регистра. Содержимое этих регистров и задает логическую функцию, заложенную внутри логического базового элемента.

Дополнительный конфигурационный регистр (на Рис. 1 справа одиночный красный квадрат) определяет потребность выдачи базового логического элемента прямо на выход значение с LUT или требуется выдать фиксированный в D-триггере показатель с LUT. Фиксация и хранение данных в цифровых схемах необходима практически в каждом разрабатываемом проекте.

Исследуя Рис. 1 как пример логического базового традиционного элемента можно видеть, насколько неограничен ресурс заложенный внутрь современного кристалла ПЛИС (SRAM-based). Конфигурационные регистры (красные квадраты) напрямую не доступны для манипуляции в цифровом проекте. Они могут только служить для строения пользовательской функции. Для одного D-триггера в разрабатываемом проекте требуется более 16 (часто намного больше) D-триггеров для хранения конфигурации ПЛИС. Логический базовый элемент в разных видах ПЛИС может быть гораздо сложнее, чем изображено на Рис. 1. Далее есть примеры из документации на разные типы ПЛИС.

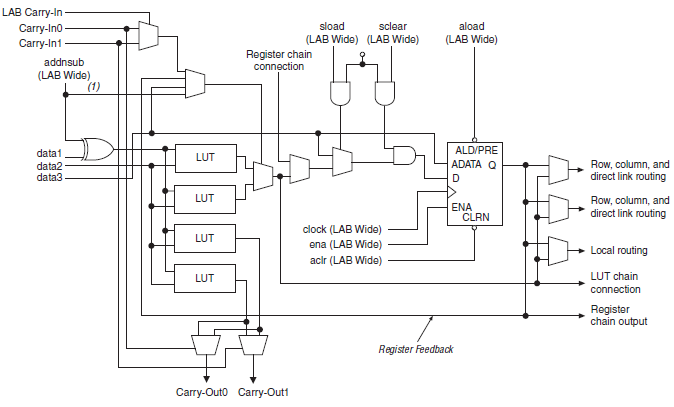

Рис. 2. Логический базовый элемент компании Альтера CPLD MAX II.

На этом рисунке можно подробно увидеть LUT и D-Триггер хранения вычислений. Ниже, на Рис. 3 показан базовый элемент Cyclone III.

Рис. 3. Логический базовый элемент компании Альтера ПЛИС Cyclone III.

В ПЛИС компании Альтера в одном LAB может содержаться 10-16 LE.

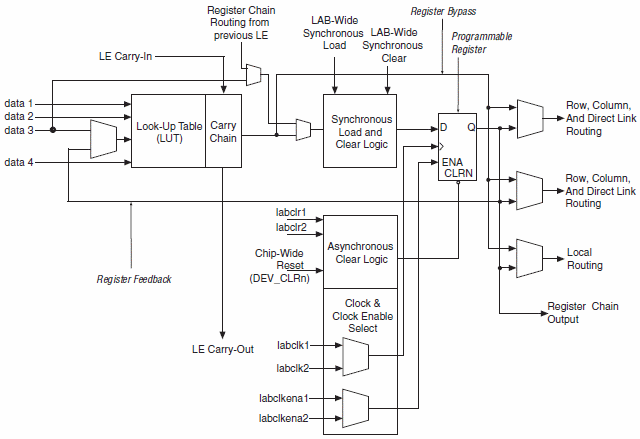

В микросхемах компании Xilinx Virtex-6 логический базовый элемент – это есть так называемый Slice, в одном CLB их находится всего два Slice. Однако один Slice – это достаточно сложное устройство:

Рис. 4. Логический базовый элемент компании Xilinx , Virtex-6 Slice.

В одном CLB Virtex-6 находится 8 LUT а так же16 D-Триггеров и еще некоторые элементы как видно на Рис.4

Другая сторона – ПЛИС компании Microsemi (ранее Actel).

Как пример, в микросхемах серии 40MX логический базовый элемент имеет такой вид:

Рис. 5. Логический базовый элемент of Microsemi 40MX serie.

Этот элемент как показано на рис.5 имеет один выход и восемь входов.

В нем не присутствует ни Look-Up Table, ни D-Триггера. Триггера, как и вся другая логика, образуются где это необходимо из таких блоков – Logic Module. В микросхемах Microsemi связь между базовыми логическими блоками обходится намного дешевле: серия 40MX может быть запрограммирована однократно. В ней межблочные связи «проплавляются» между соединяющими дорожками и больше не могут быть изменены. Не имеется регистров для временного хранения задаваемой «прошивки». Тут нет программируемых мультиплексоров, как в ПЛИС других типов. Это технология имеет название antifuse – для производства таких микросхем используется измененный сложный техпроцесс CMOS с дополнительными слоями для создания межблочных связей.

3.4 Программируемые связи логических блоков.

Для того что бы в ПЛИС начала функционировать необходимая цифровая схема , нужно сконфигурировать логические блоки которые мы имеем специальным образом, а так же необходимо создать и запрограммировать связи между логическими блоками.

В ПЛИС для этого имеются особые конфигурируемые коммутаторы.

В технической документации на английском языке не редко встречаются такие термины: FPGA Routing Architecture и Programmable Routing Interconnect. Это обозначение программируемых связей между логическими блоками.

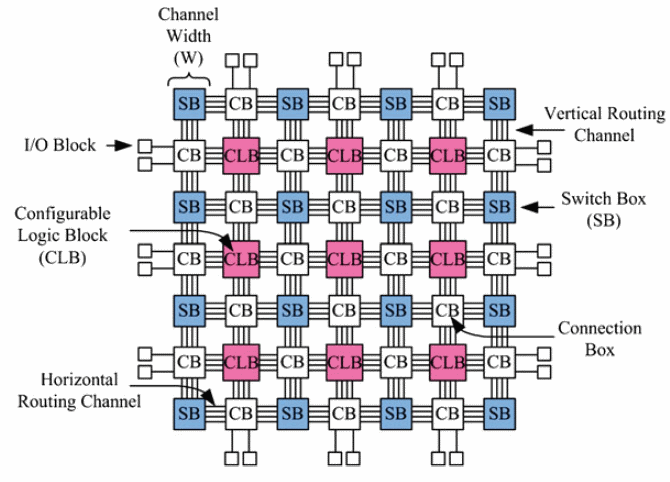

Известны две базовые методики конфигурации ПЛИС по типу архитектуры связей: иерархическая и островная.

Рис. 6. Островная архитектура ПЛИС.

Островная FGPA имеет такое название потому, что создаваемые блоки все между собой равны и находятся, «как острова в океане», между узлами коммутации и линиями связи.

На Рис. 6 обозначаются «острова» CB – Connection Box и SB – Switch Box. По сути это это есть программируемые мультиплексоры, подключающие тот или иной CLB к другому CLB через определенные проводные соединения в ПЛИС.

Это так называемый island-style FPGA или же по-другому mesh-based FPGA. Примером таких типичных микросхем может служить серии Altera Cyclone и Stratix.

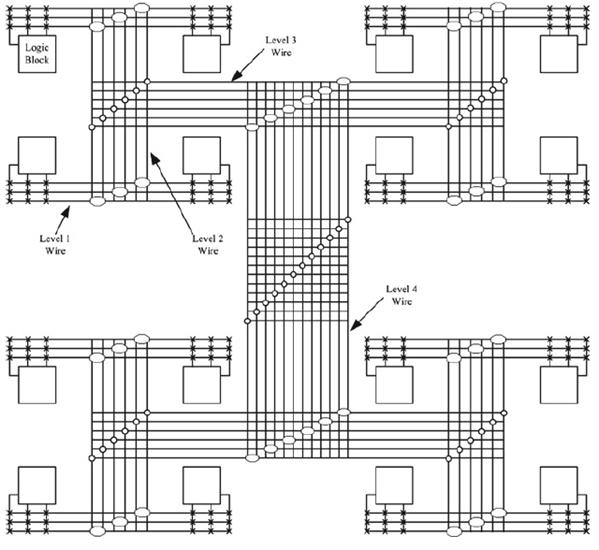

Другой известный тип ПЛИС – это иерархические ПЛИС. Расчет идет на то, что в схеме всегда имеются зоны которые взаимодействуют друг с другом наиболее тесно, чем с другими отдаленными модулями проекта.

Рис. 7. Иерархическая ПЛИС.

Как видно на рисунке близлежащие CLB соединить очень просто, необходимо не много коммутаторов и полученные связи работают достаточно быстро. Но если необходим значительно большой блок вычислителей, то сигналу необходимо выйти на более высокую степень иерархии а затем зайти вглубь в соседнюю «комнату».

Говорить о том что данный метод хуже, чем island-style, нельзя. Так как каждый метод имеет свои достоинства и недостатки.

Типичные представители ПЛИС с иерархичным строением – это микросхемы Альтера серии Flex10K, APEX.

3.4 Компилятор для проектирования ПЛИС.

ПО (программное обеспечение) для проектирования ПЛИС, конкретно компилятор (синтезатор логики и фиттер и ассемблер) – самая сложная часть всей ПЛИС технологии.

Компилятору нужно проанализировать разработаный проект (текстовые описания и схемы реализованный на Verilog HDL или VHDL ) и сгенерировать нетлист (netlist) – наименования всех компонентов схемы и связи между ними. Netlist должен быть правильно оптимизирован – логические функции необходимо минимизировать, продублированные регистры необходимо удалить.

После этого компилятор должен поместить всю спроектированную логику из netlist в имеющуюся архитектуру ПЛИС. Этим занимается фиттер (fitter). Он размещает логические элементы и выполняет трассировку связей между ними (процесс называется place and route). Трудность заключается в том, что сущствуют разные способы размещения проектав ПЛИС и таких способов миллионы. Некоторое размещение и трассировка могут быть лучше, другие хуже. Главный критерий качества полученной системы – максимальная рабочая частота, на которой сможет работать проект при таком размещении элементов и при данной трассировке связей. На это оказывает влияние длина соединений между логическими блоками и число программируемых коммутаторов между ними.

Компилятор выдает отчет о времени проходдения сигналов от регистра до регистра по результатам работы. Такая информация является часто полезной для разработчика высокопроизводительных систем. Разработчик для ПЛИС имеет возможность корректировать работу компилятора, давать ему советы, где в каком месте кристалла лучше расположить определенный модуль проекта.

При выборе для своего проекта, для своей разрабатываемой платы определенные микросхемы ПЛИС разработчик в какой-то мере попадает в зависимость от производителя данной ПЛИС, так как в работе обязан пользоваться ПО от этого же производителя.

Программное обеспечение компании Альтера: Quartus II.

ПО Xilinx для проектирования для ПЛИС: ISE Suite, Vivaldo Design Suite.

ПО компании Microsemi: Libero IDE, Libero SoC.

Программное обеспечение, компиляторы для ПЛИС – это, возможно, важнейшая составляющая интеллектуальной собственности компаний производителей ПЛИС.

4. ЭЛЕМЕНТНАЯ БАЗА И ПО.

4.1 Элементная база

4.1.1 Выбор ПЛИС

В качесте основного элемента разрабатываемой СКЗИ служит FPGA - Программируемая вентильная матрица FPGA - Программируемая вентильная матрица FPGA - Cyclone III E 1395 LABs 153 IOs EP3C40F780C6 FPGA , ниже приведены технические характеристики.

| Производитель: | Altera |

| Категория продукта: | FPGA - Программируемая вентильная матрица |

| Продукт: | Cyclone III E |

| Количество логических элементов: | 22320 |

| Количество блоков логических массивов (LAB): | 1395 |

| Количество входов/выходов: | 153 I/O |

| Рабочее напряжение питания: | 1 V to 1.2 V |

| Максимальная рабочая температура: | + 70 C |

| Вид монтажа: | SMD/SMT |

| Упаковка / блок: | FBGA-256 |

| Торговая марка: | Altera Corporation |

| Максимальная рабочая частота: | 200 MHz |

| Минимальная рабочая температура: | 0 C |

| Упаковка: | Tray |

| Серия: | EP4CE22 Cyclone III E |

| Общий объем памяти: | 594 kbit |

| Коммерческое обозначение: | Cyclone III |

4.1.2 Выбор отладочной платы

Так же для отладки разработанных проектов была вбрана отладочная плата на базе данной ПЛИС.

Краткие характеристики:

1. Cyclone® III EP3C40F780C6 FPGA

· 22,320 Logic elements (LEs)

· 594 Embedded memory (Kbits)

· 66 Embedded 18 x 18 multipliers

· 4 General-purpose PLLs

· 153 Maximum FPGA I/O pins

· On-board USB-Blaster circuit for programming

· FPGA Serial Configuration Device (EPCS)

2. Expansion Header

· Two 40-pin Headers (GPIOs) provides 72 I/O pins

· One 26-pin header provides 16 digital I/O pins and 8 analog input pins to connect to analog sensors, etc

3. Memory Devices

· 32MB SDRAM

· 2Kb I2C EEPROM

4. General User Input/Output

· 8 green LEDs

· 2 debounced push-buttons

· 4 dip switches

5. G-Sensor

· ADI ADXL345, 3-axis accelerometer with high resolution (13-bit)

6. A/D Converter

· NS ADC128S022, 8-Channel, 12-bit A/D Converter

7. Clock System

· On-board 50MHz clock oscillator

4.2 Программное обеспечение

Так как для реализации СКЗИ была выбрана ПЛИС компании Altera, поэтому компилятор для создания проекта был выбран Quartus II 9.0. ПО Quartus II является автоматизированной системой сквозного проектирования цифровых устройств на кристаллах ПЛИС фирмы Altera . Оно предоставляет пользователю достаточно широкие возможности по созданию проекта, логическому синтезу, компиляции проекта, программированию ПЛИС, функциональному и временному моделированию, временному анализу и анализу потребляемой мощности проекта, реализации внутрисистемной отладки.

В Quartus II заложен удобный графический интерфейс и не сложная в применении система справок, которая содержит в себе всю необходимую для выполнения проектирования информацию. Также пакет дает возможность использовать командную строку для выполнения каждого этапа проектирования. Причем, в зависимости от пожеланий пользователя, графический интерфейс или командная строка имеют возможность использоваться как для исполнения отдельных этапов, так и для всего проекта в целом.

Пакет Quartus II содержит в себе огромное количество программных модулей, предназначенных для помощи в выполнении различных этапов проектирования. Задание параметров и выполнение типовых команд выполняется в отдельных модулях однотипно, что значительно облегчает работу пользователя. Редакторы исходных файлов проекта (графический, текстовый, редактор символов, содержимого модулей памяти, временных диаграмм, конечных автоматов) используют одинаковые подходы и приёмы, а также похожие оконные формы, применяемые при создании и редактировании исходных файлов с описанием модулей проектируемого устройства.

В одном иерархическом проекте можно сочетать использование различных типов описания исходных файлов модулей проекта, подбирая наиболее подходящий тип, для каждого модуля.

В состав стандартной библиотеки Quartus II входит большое количество базовых элементов, включая мегафункции и макрофункции. Составной частью мегафункций являются операционные устройства, созданные по стандарту библиотеки параметризируемых модулей ( LPM – library of parameterized modules).

Значительная часть мегафункций разработана фирмой Altera. Они описаны на языке низкого уровня и оптимизированы для применения в ПЛИС компании Altera. Остальная часть разработана компаниями партнерами. Применение мегафункций в проектах пользователя значительно расширит возможности проектирования и ускорит выполнение проекта.

Пакет Quartus II имеет с составе средство SOPC (System on programmable chip) Builder, которое предназначено для разработки реализуемых на кристалле процессорных систем . При помощи этого средства можно легко создавать конфигурируемые процессорные ядра, реализовывать на кристалле различные контроллеры, а также значительную часть периферийного оборудования.

4.3 Обоснование выбора элементной базы и ПО.

В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). Для программирования используются программаторы и отладочные среды, позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках описания аппаратуры: Verilog, VHDL, AHDL и др., Фирмы изготовители ПЛИС для разработки проектов на своих микросхемах выпускают привязанное ним ПО. Поэтому выбирая микросхему мы выбираем и ПО в которой будем с ней работать . Выбор же самой ПЛИС обуславливался ТТХ , для реализации на ней проекта СКЗИ.

КОНСТРУКТОРСКАЯ ЧАСТЬ

1.РАЗРАБОТКА ПРОЕКТА ГОСТ 28147-89 ДЛЯ ПРОГРАММИРОВАНИЯ ПЛИС

1.1 Режим простой замены

1.1.1 Зашифрование открытых данных

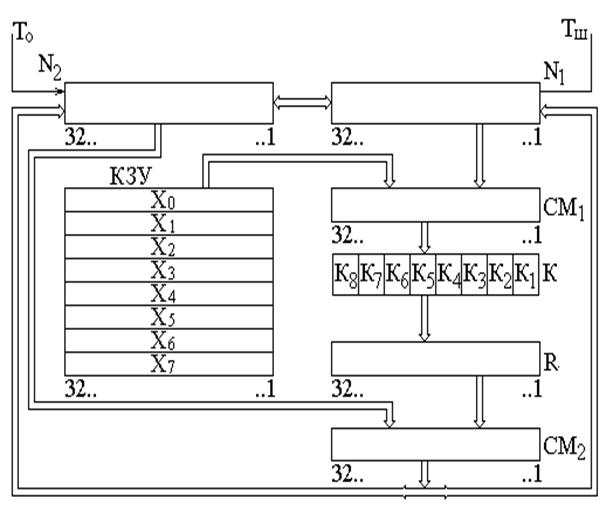

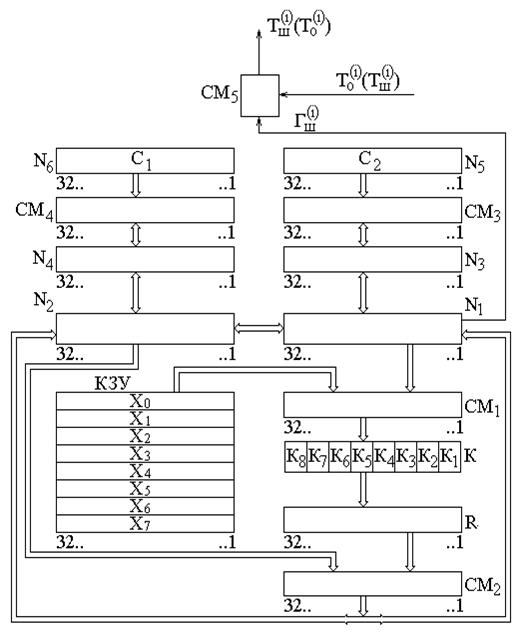

Криптосхема, реализующая алгоритм зашифрования в режиме простой замены, должна иметь вид, приведенный на рисунке 1а.

Рисунок 1а.

Открытые данные, подлежащие зашифрованию, разбиваются на блоки по 64 бита в каждом. Ввод любого блока Т0=(a1(0), a2(0), …, a32(0), b1(0), b2(0), …, b32(0)) двоичной информации в накопители N1 (рис3 ) и N2 (рис5) производится так:

что значение a1(0) вводится в 1-й разряд N1,

значение a2(0) вводится во 2-й разряд N1, и т.д.,

значение a32(0) вводится в 32-й разряд N1;

значение b1(0) вводится в 1-й разряд N2,

значение b2(0) вводится во 2-й разряд N2 и т.д.,

значение b32(0) вводится в 32-й разряд N2.

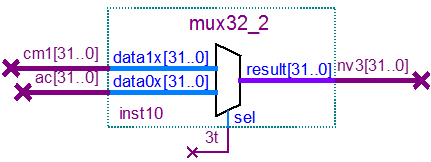

Блоки данных вводятся через мультиплексоры (рис 2 и рис 4) чтобы корректно записывать в накопители зашифрованные данные и только поступившие - открытые данные.

В результате получают состояние (a32(0), a31(0), …, a2(0), a1(0)) накопителя N1 и состояние (b32(0), b31(0), …, b2(0), b1(0)) накопителя N2.

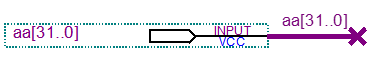

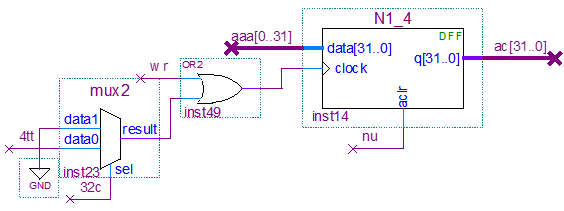

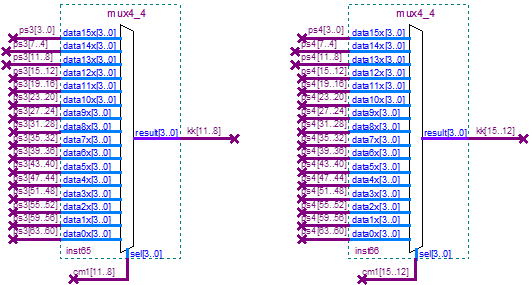

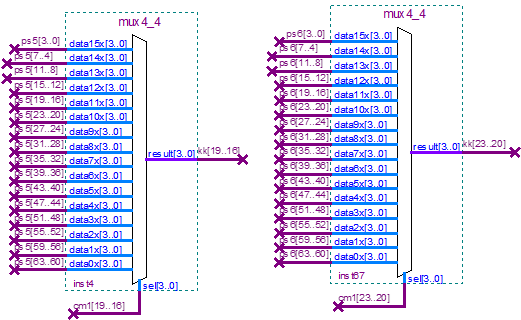

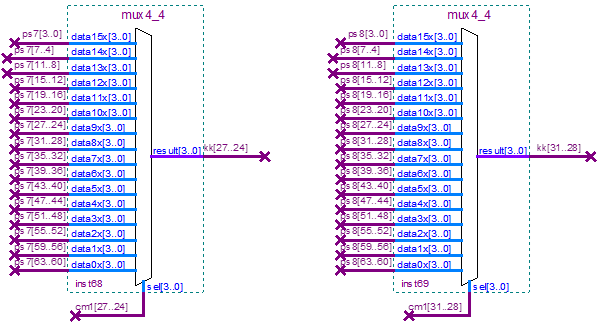

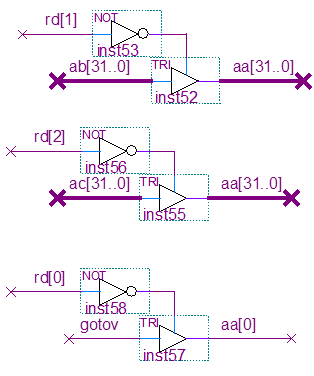

Рис.1 Поступающие данные для записи

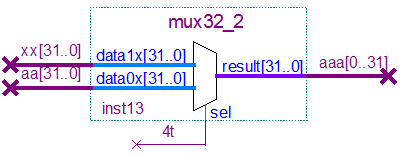

Рис2. Мультиплексор обрабатывающий поступающую информацию для накопителя N1

- xx [31..0]- блок информации полученный после цикла зашифрования

-aa [31..0]- блок информации полученный для цикла зашифрования

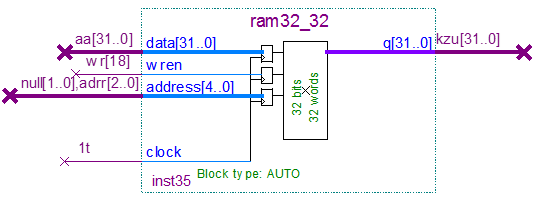

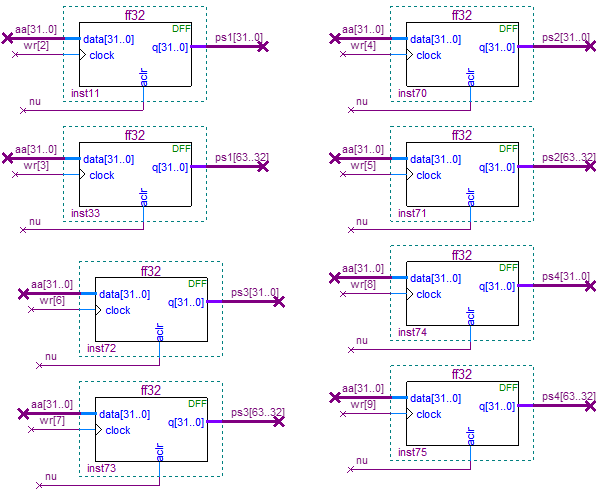

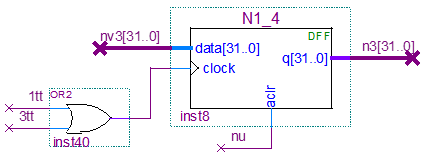

Рис3. Накопитель N1 в который записывается блок двоичной информации Т0=(a1(0), a2(0), …, a32(0)

Рис4. Мультиплексор обрабатывающий поступающую информацию для накопителя N2

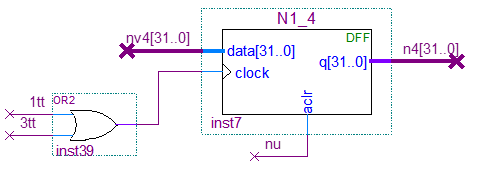

-bl [31..0]- блок информации переписываемый из носителя N1 при записывании в него xx[31..0]

Рис5. Накопитель N2 в который записывается блок двоичной информации

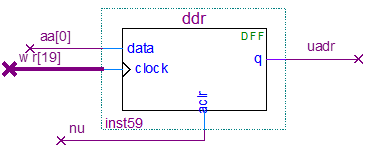

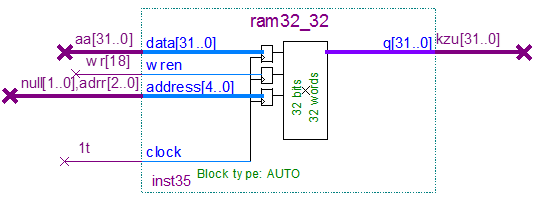

В КЗУ (рис 7.) вводятся 256 бит ключа (рис 8.) . Чтобы обеспечить ввод ключа в КЗУ необходимо установить счетчик (рис 6) на котором по команде wr[19] к изменению данных откроется доступ, т.е a[0] =1, после записи ключа a[0] становится в 0. Далее схема зашифрования готова к работе.

Рис.6 Счетчик записи ключа в КЗУ

Содержимое восьми 32-разрядных накопителей Х0, Х1, …, Х7 имеет вид:

Х0=(W32, W31, …, W2, W1)

Х1=(W64, W63, …, W34, W33)

. . . . . . . . . . . . .

Х7=(W256, W255, …, W226, W225)

Рис7. Носитель КЗУ в который вводятся 256 бит ключа.

Рис8. Ключ зашифрования.

Алгоритм зашифрования 64-разрядного блока открытых данных в режиме простой замены состоит из 32 циклов.

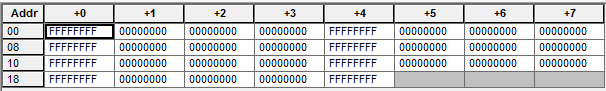

В первом цикле начальное заполнение накопителя N1 суммируется по модулю 232 в сумматоре СМ1 (Рис. 9) с заполнением накопителя Х0, при этом заполнение накопителя N1 сохраняется.

Рис9. Сумматор СМ1

ac[31..0] –данные полученные из носителя N1

Рис10. Блоки подстановки K0 ..K7

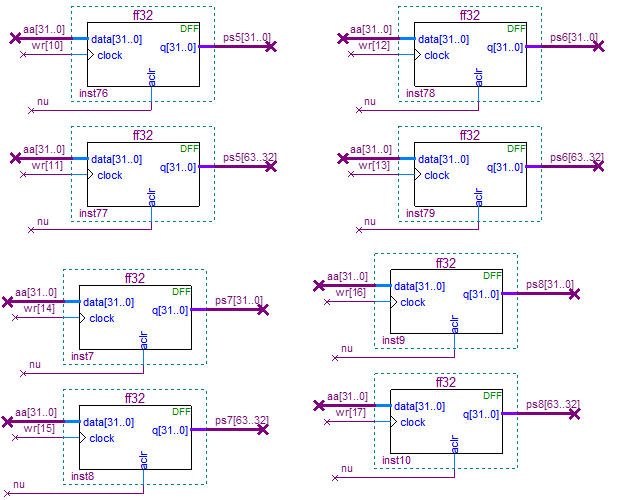

Рис. 11 Регистры заполнения данных перестановки для блоков K0 ..K7

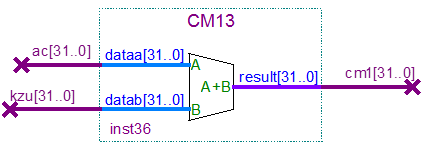

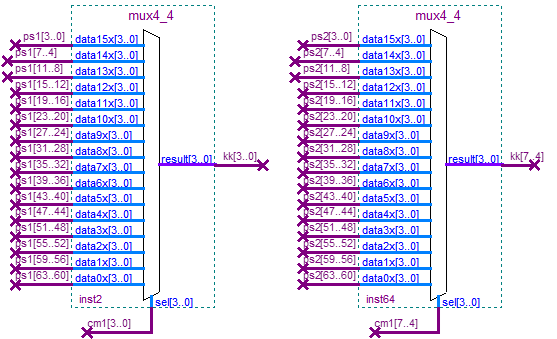

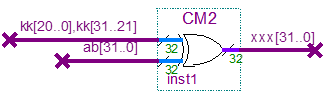

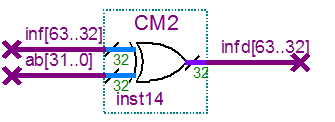

Заполнение блоков подстановки K0 ..K7 (рис.10) происходит через регистры (рис 11) с помощью поступающих команд wr[2..17] .Результат суммирования преобразуется в блоке подстановки К и полученный вектор поступает на вход регистра R, где циклически сдвигается на одиннадцать шагов в сторону старших разрядов. Результат сдвига суммируется поразрядно по модулю 2 в сумматоре СМ2 (рис 12) с 32-разрядным заполнением накопителя N2.

Рис12. Сумматор СМ2

kk[20..0],kk[31..21]-сдвиг в 11 разрядов условно переставлены биты.

Полученный в СМ2 результат записывается в N1, при этом старое значение N1 переписывается в N2. Первый цикл заканчивается.

Последующие циклы осуществляются аналогично, при этом во 2-м цикле из КЗУ считывается заполнение Х1, в 3-м цикле из КЗУ считывается заполнение Х2 и т.д., в 8-м цикле из КЗУ считывается заполнение Х7. В циклах с 9-го по 16-й, а также в циклах с 17-го по 24-й заполнения из КЗУ считываются в том же порядке:

Х0, Х1, Х2, Х3, Х4, Х5, Х6, Х7.

В последних восьми циклах с 25-го по 32-й порядок считывания заполнений КЗУ обратный:

Х7, Х6, Х5, Х4, Х3, Х2, Х1, Х0.

Таким образом, при зашифровании в 32 циклах осуществляется следующий порядок выбора заполнений накопителей:

Х0, Х1, Х2, Х3, Х4, Х5, Х6, Х7, Х0, Х1, Х2, Х3, Х4, Х5, Х6, Х7,

Х0, Х1, Х2, Х3, Х4, Х5, Х6, Х7, Х7, Х6, Х5, Х4, Х3, Х2, Х1, Х0.

В 32-м цикле результат из сумматора СМ2 вводится в накопитель N2, а в накопителе N1 сохраняется старое заполнение.

Полученные после 32-го цикла зашифрования заполнения накопителей N1 и N2 являются блоком зашифрованных данных, соответствующих блоку открытых данных.

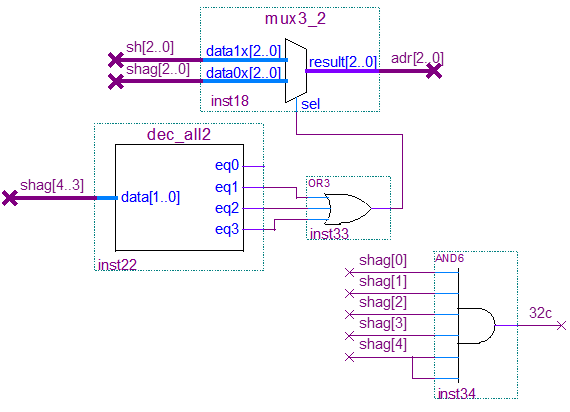

Рис.13 Счетчик на 32 цикла

При завершении 32 циклов зашифрования , записаная информация передается на выход и сбрасывается , алгоритм запускается по новой уже с новыми блоками информации. После того как проходит 32 цикл , процессор засекает переключение по rd[0] (рис 14) с 0 на 1 , после этого обращается к rd[1] , rd[2] и читает зашифрованую информацию.

Рис.14

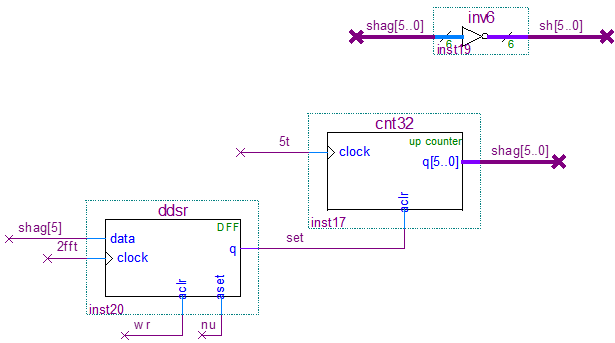

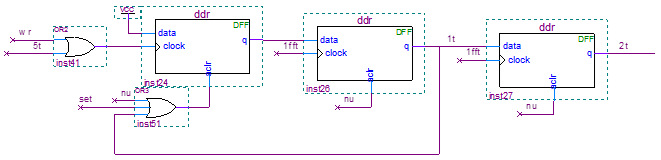

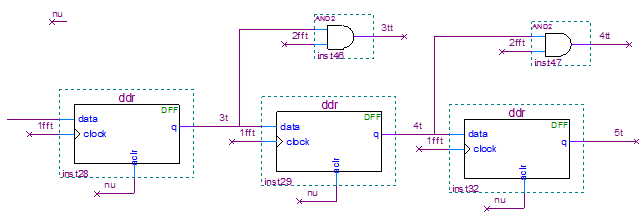

Работа алгоритма на ПЛИС осуществляется в 5 тактов, которые формируются с помощью на D-триггеров , логическая схема формирования тактов указана на рисунке 15

Рис. 15 Формирование тактовых сигналов.

-Первый такт обеспечивает вывод ключа(1t)

-Второй такт Фиксирует выход СМ2 (2t)

-Третий переключает мультиплексор и записывает результат в N2 (3t)

-Четвертый такт работает аналогично с N1 (4t)

-Пятый такт срабатывает по завершению 32 циклов и сбрасывает информацию. (5t)

1.1.2 Расшифрование зашифрованных данных в режиме простой замены

Криптосхема, реализующая алгоритм расшифрования в режиме простой замены, имеет тот же вид (см. рисунок 2), что и при зашифровании. В КЗУ вводятся 256 бит того же ключа, на котором осуществлялось зашифрование. Зашифрованные данные, подлежащие расшифрованию, разбиты на блоки по 64 бита в каждом.

Ввод любого блока Тш=(а1(32), а2(32), …, а32(32),

b1(32), b2(32), …,

b32(32)) в накопители N1 и N2 производится так,

что значение а1(32) вводится в 1-й разряд N1,

значение a2(32) вводится во 2-й разряд N1,

и т.д., значение a32(32) вводится в 32-й разряд N1;

значение b1(32) вводится в 1-й разряд N2, значение b2(32) вводится во 2-й разряд N2 и т.д.,

значение b32(32) вводится в 32-й разряд N2.

Расшифрование осуществляется по тому же алгоритму, что и зашифрование открытых данных, с тем изменением, что заполнения накопителей Х0, Х1, …, Х7 считываются из КЗУ в циклах расшифрования в следующем порядке:

Х0, Х1, Х2, Х3, Х4, Х5, Х6, Х7, Х7, Х6, Х5, Х4, Х3, Х2, Х1, Х0,

Х7, Х6, Х5, Х4, Х3, Х2, Х1, Х0, Х7, Х6, Х5, Х4, Х3, Х2, Х1, Х0.

Полученные после 32 циклов работы заполнения накопителей N1 и N2 составляют блок открытых данных.

Т0=(a1(0), a2(0), …, a32(0), b1(0), b2(0), …, b32(0)), соответствующий блоку зашифрованных данных,

при этом значение а1(0) блока Т0 соответствует содержимому 1-го разряда N1, значение а2(0) соответствует содержимому 2-го разряда N1 и т.д.,

значение а32(0) соответствует содержимому 32-го разряда N1;

значение b1(0) соответствует содержимому 1-го разряда N2, значение b2(0) соответствует содержимому 2-го разряда N2, и т.д.,

значение b32(0) соответствует содержимому 32-го разряда N2.

Аналогично расшифровываются остальные блоки зашифрованных данных.

2. Режим гаммирования

2.1.1. Зашифрование открытых данных в режиме гаммирования

Криптосхема, реализующая алгоритм зашифрования в режиме гаммирования, должна иметь вид, приведенный на рисунке 1б.

Рисунок 1б

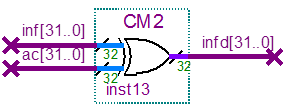

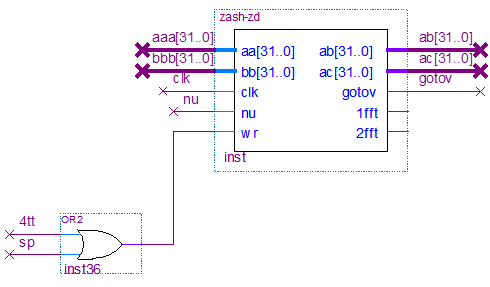

Открытые данные, разбитые на 64-разрядные блоки Т0(1), Т0(2), …, Т0(М-1), Т0(М), зашифровываются в режиме гаммирования путем поразрядного суммирования по модулю 2 в сумматоре СМ5 (рис 1) с гаммой шифра Гш, которая вырабатывается блоками по 64 бита:

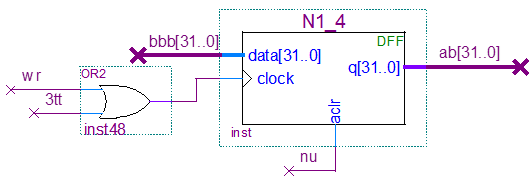

Рис. 1 Сумматор СМ5 где:

inf[63…32]- гамма шифра Гш

ab[31…0] – зашифрованные данные , подготовленные для побитного сложения с гаммой шифра Гш

Гш=(Гш(1), Гш(2), …, Гш(М-1), Гш(М)),

где М – определяется объемом шифруемых данных.

Гш(i) – i-й 64-разрядный блок, i=1÷Ì, число двоичных разрядов в блоке Т0(М) может быть меньше 64, при этом неиспользованная для зашифрования часть гаммы шифра из блока Гш(М) отбрасывается.

Рис2. КЗУ.

В КЗУ (Рис.2) вводятся 256 бит ключа. В накопители N1, N2 вводится 64-разрядная двоичная последовательность (синхропосылка) S=(S1, S2, …, S64), являющаяся исходным заполнением этих накопителей для последующей выработки М блоков гаммы шифра.

Синхропосылка вводится в N1 и N2 так, что значение S1 вводится в 1-й разряд N1, значение S2 вводится во 2-й разряд N1, и т.д.,

значение S32 вводится в 32-й разряд N1;

значение S33 вводится в 1-й разряд N2,

значение S34 вводится во 2-й разряд N2 и т.д.,

значение S64 вводится в 32-й разряд N2.

Исходное заполнение накопителей N1 и N2 (синхропосылка S) зашифровывается в режиме простой замены . Результат зашифрования переписывается в 32-разрядые накопители N3 (рис 3) и N4 (рис 4) так, что заполнение N1 переписывается в N3, а заполнение N2 переписывается в N4.

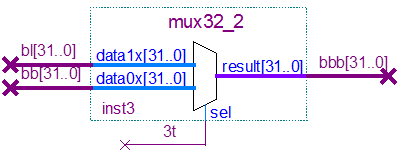

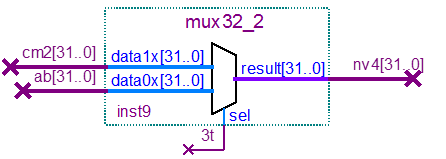

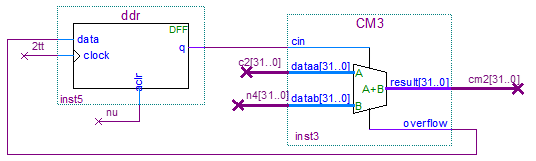

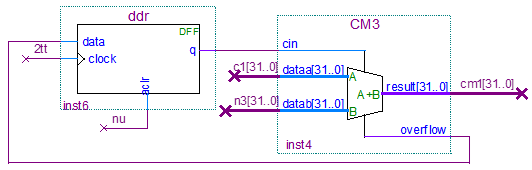

Рис 3. Мультиплексор и накопитель N3 для переключения записи из N1 , и записи просуммированной информации из СМ3

Рис. 4 Мультиплексор и накопитель N4 для переключения записи из N2 , и записи просуммированной информации из СМ4

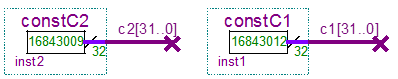

Заполнение накопителя N4 суммируется по модулю (232-1) в сумматоре СМ4 с 32-разрядной константой С1 из накопителя N6, результат записывается в N4.

Рис. 5 Константы С1 и С2

Заполнение накопителя N3 суммируется по модулю 232 в сумматоре СМ3 (рис 6) с 32-разрядной константой С2 из накопителя N5, результат записывается в N3.

Рис. 6 Сумматор СМ3

Рис. 7 Сумматор СМ4

Суммирование в СМ3 и СМ4 проходит на 2 такте

Заполнение N3 переписывается в N1, а заполнение N4 переписывается в N2, при этом заполнение N3, N4 сохраняется.

Заполнение N1 и N2 зашифровывается в режиме простой замены(п.1.1 переход на схему рис 8) .

Рис. 8 Переход на схему шифрования в режиме простой замены

Полученное в результате зашифрования заполнение N1, N2 образует первый 64-разрядный блок гаммы шифра Гш(1), который суммируется поразрядно по модулю 2 в сумматоре СМ5 с первым 64-разрядным блоком открытых данных Т0(1)=(t1(1), t2(1), …, t63(1), t64(1)). В результате суммирования получается 64-разрядный блок зашифрованных данных Тш(1)=(τ1(1), τ2(1), …, τ63(1), τ64(1)).

Значение τ1(1) блока Тш(1) является результатом суммирования по модулю 2 в СМ5 значения t1(1) из блока Т0(1)

со значением 1-го разряда N1, значение τ2(1) блока Тш(1) является результатом суммирования по модулю 2 в СМ5 значения t2(1) из блока Т0(1)

со значением 2-го разряда N1 и т.д., значение τ64(1) блока Тш(1) является результатом суммирования по модулю 2 в СМ5 значения t64(1) из блока Т0(1) со значением 32-го разряда N2.

Для получения следующего 64-разрядного блока гаммы шифра Гш(2) заполнение N4 суммируется по модулю (232-1) в сумматоре СМ4 с константой С1 из N6, заполнение N3 суммируется по модулю 232 в сумматоре СМ3 с константой С2 из N5. Новое заполнение N3 переписывается в N1, а новое заполнение N4 переписывается в N2, при этом заполнение N3 и N4 сохраняется.

Заполнение N1 и N2 зашифровывается в режиме простой замены. Полученное в результате зашифрования заполнение N1, N2 образует второй 64-разрядный блок гаммы шифра Гш(2), который суммируется поразрядно по модулю 2 в сумматоре СМ5 со вторым блоком открытых данных Т0(2). Аналогично вырабатываются блоки гаммы шифра Гш(3), Гш(4) …, Гш(М) и зашифровываются блоки открытых данных Т0(3), Т0(4) …, Т0(М). Если длина последнего М-го блока открытых данных Т0(М) меньше 64 бит, то из последнего М-го блока гаммы шифра Гш(М) для зашифрования используется только соответствующее число разрядов гаммы шифра, остальные разряды отбрасываются.

В канал связи или память ЭВМ передаются синхропосылка S и блоки зашифрованных данных Тш(1), Тш(2) …, Тш(М).

4.4.2. Расшифрование зашифрованных данных в режиме гаммирования

При расшифровании криптосхема имеет тот же вид, что и при зашифровании .В КЗУ вводятся 256 бит ключа, с помощью которого осуществлялось зашифрование данных Т0(1), Т0(2) …, Т0(М) при этом Т0(М) может содержать меньше 64 разрядов.