«Южно–Российский Государственный Технический

Министерство образования и науки Российской Федерации

Федеральное агентство по образованию

Государственное образовательное учреждение высшего профессионального образования

«Южно–Российский Государственный Технический

Университет (Новочеркасский политехнический институт)»

Кафедра автоматики и телемеханики

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

к лабораторным работам по курсу

«Основы научных исследований. Исследование цифровых систем

на основе ПЛИС»

Новочеркасск 2010 г.

УДК 621.38

Рецензент

Составители: Лачин В.И., Соломенцев К.Ю.

Методические указания к лабораторным работам по курсу «Основы научных исследований. Исследование цифровых систем на основе ПЛИС». /Южно-Российский государственный технический университет. Новочеркасск: ЮРГТУ, 2009, ___ с.

Методические указания содержат цели, программы и методические указания для выполнения лабораторных работ по исследованию цифровых систем на основе ПЛИС. Методические указания предназначены для выполнения лабораторных работ по курсу «Основы научных исследований. Исследование цифровых систем на основе ПЛИС» студентами 5-го курса специальностей 220201 – «Управление и информатика в технических системах» и 210106 – «Промышленная электроника» дневной формы обучения.

© Южно-Российский государственный технический университет (НПИ), 2010.

1. Общие сведения о программируемых логических интегральных схемах

Программируемые логические интегральные схемы (ПЛИС) представляют собой интегральные схемы, которые могут программироваться пользователем для выполнения заданной функции. Для реализации комбинационных схем достаточно давно применяются программируемые логические матрицы (ПЛМ) [1].

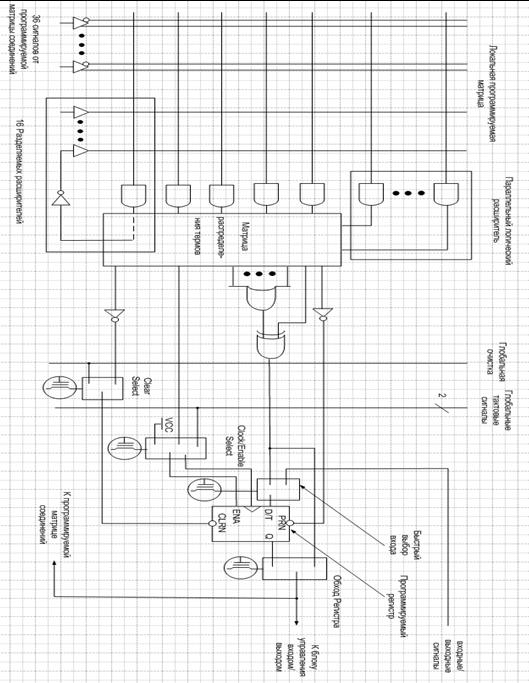

Структура типовой ПЛИС приведена на рисунке 1.1. Схема имеет N триггерных ячеек ТЯ.1, ТЯ.2 ... ТЯ.N, M информационных входов I.1, I.2 ... I.M и вход синхронизации C. Выходы триггерных ячеек подключены к контактам I/O.1, I/O.2 ... I/O.N, которые могут программироваться в качестве входов или выходов в зависимости от структуры разрабатываемой схемы. Прямые и инверсные значения выходов триггерных ячеек, информационных входов и сигнала синхронизации подключены к логическому массиву соединений, выходами которого являются элементарные конъюнкции (термы) P.i.

К каждой триггерной ячейке подключается K выходов логического массива P.1, P.2 ... P.K. На рисунке 1.2 приведена схема триггерной ячейки. В состав триггерной ячейки входит триггер (обычно D-триггер), элемент ИЛИ, на входы которого подключается K термов P.1 ... P.K с выхода логического массива, схема сложения по модулю два М2, переключатели K1 и K2. На управляющий вход триггера поступает сигнал Q.D, формируемый в виде дизъюнктивных нормальных форм с возможностью инверсии на схеме М2. Синхронизация триггера обычно осуществляется от общего сигнала C. Во многих схемах предусмотрена возможность задания сигнала синхронизации из логического массива.

Рисунок 1.1 – Структура ПЛИС

Рисунок 1.2 – Триггерная ячейка

Переключатель K1 позволяет выдавать на выходной контакт как выход триггера Q, так и управляющий вход - Q.D. Сигнал OE=1 разрешает прохождение сигнала с контакта K1 на выход I/O.i. При OE=0 контакт I/O.i может при необходимости использоваться в качестве входа. Переключатель K2 определяет сигнал обратной связи F.i в логический массив: это может быть выход триггера или сигнал, поступающий на контакт I/O.i при использовании его в качестве входного. В ряде микросхем может использоваться двойная обратная связь F1.i и F2.i (рисунок 1.3), при использовании которой в случае, если выход триггера не выводится на контакт микросхемы, в логический массив соединений могут одновременно подключаться выход триггера Q (или его вход - Q.D) и контакт I/O.i, используемый как вход. Сигнал OE в этом случае равен нулю, т. е. запрещает прохождение сигнала с переключателя K1 на I/O.i. При необходимости при соответствующих положениях K1 и K2 в обратную связь могут поступать одновременно сигналы Q и Q.D.

Рисунок 1.3 – Триггерная ячейка с двойной обратной связью

На рисунке 1.4 показана упрощенная схема логического массива соединений. Каждый из сигналов F.1 ... F.N и I.1 ... I.K при необходимости может подключаться к любой из горизонтальных линий P1.1 ... PK.N. На выходах последних вырабатываются элементарные логические произведения (термы). Похожая организация используется в программируемых логических матрицах.

Рисунок 1.4 – Логический массив

Для создания конкретной схемы ПЛИС должна быть запрограммирована внешними схемами. При этом программируются как логический массив, так и триггерные ячейки [2]. При программировании ПЛИС могут использоваться четыре варианта: однократно прожигаемые перемычки, электрически программируемые элементы с ультрафиолетовым стиранием, электрически перепрограммируемые элементы памяти и программируемые структуры на базе ЗУ с произвольной выборкой.

1. Основные характеристики ПЛИС Altera:

1) логическая емкость, количество эквивалентных вентилей 1250;

2) число макроячеек 64;

3) число логических блоков 4;

4) число программируемых пользователем выводов 68;

5) задержка распространения сигнала вход-выход, tpd 5 нс;

6) время установки глобального тактового сигнала, tsu 2,9 нс;

7) задержка глобального тактового сигнала до выхода, tco1 3,2 нс;

8) максимальная глобальная тактовая частота, fcnt 175,4МГц;

EPM7064S может поставляться в корпусах различного типа. В таблице 2.1 приведены все возможные варианты.

Таблица 2.1 - Возможные корпуса микросхемы EPM7064S

| Число программируемых пользователем выводов | Тип корпуса |

| 36 | 44-Pin PLCC |

| 36 | 44-Pin TQFP |

| 68 | 84-Pin PLCC |

| 68 | 100-Pin TQFP |

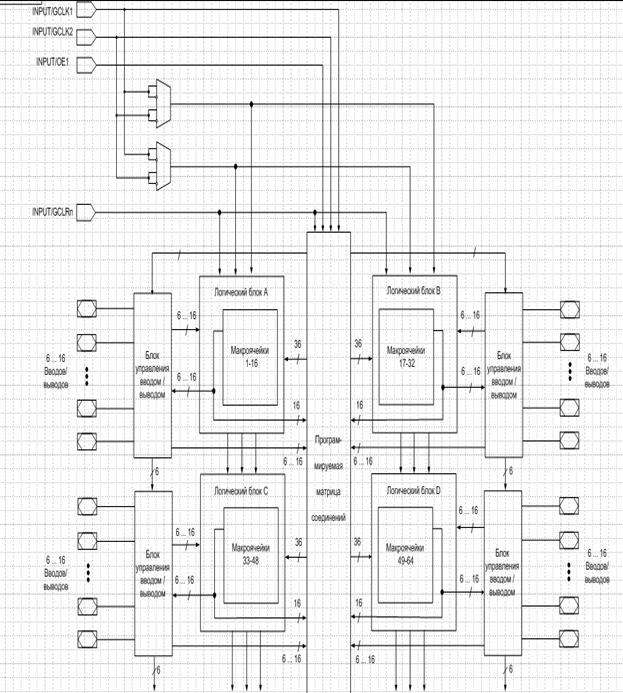

EPM7064S содержит 64 макроячейки (МА), которые могут быть объединены в группы по 16 единиц. Такое объединение носит название логический блок (Logic Array Block - LAB). В каждой МА находятся программируемая матрица “И”, фиксированная матрица “ИЛИ” и конфигурационные регистры с независимым управлением. Для увеличения функциональности МА, входящие в один логический блок, могут быть объединены при помощи разделяемого и параллельного расширителей. Это позволяет реализовывать логические функции с 32 переменными. МЯ изготовлены по технологии CMOS EEPROM.

2. Функционнальная схема ПЛИС фирмы Altera

3. C труктурная схема макроячейки