III. Третья часть курсового проекта

Этап 1. Идея.

Задача: спроектировать микропрограммный автомат на перепрограммируемом постоянном запоминающем устройстве ППЗУ, который должен формировать микропрограмму, выполняющую заданную операцию на РАЛУ центрального процессора.

Код операции АЛУ выбирается по пяти последним цифрам PIN-кода:

100 10001

100 10001

Любой алгоритм можно реализовать тремя способами:

- если задача простая, то нужно построить таблицу истинности, составить систему логических уравнений и реализовать её в жесткой логике

- для более сложных задач мы можем записать таблицу истинности прямо в память устройства — это микропрограммная реализация алгоритма на памяти

- мы можем взять готовую вычислительную машину и реализовать алгоритм программированием

Для этой части курсового проекта выберем второй способ.

Таблица операций АЛУ.

К семидесятым годам прошлого века установился типовой набор операций АЛУ, позволяющий строить команды центрального процессора для любых практических задач, которые существуют.

К семидесятым годам прошлого века установился типовой набор операций АЛУ, позволяющий строить команды центрального процессора для любых практических задач, которые существуют.

Всего в АЛУ входит 16 арифметических (не блокируются цепи переноса из младших разрядов в старшие) и 16 логических операций (блокируются цепи переноса из младших разрядов в старшие).

Разряды операндов обрабатываются побитно.

MO — арифметическая или логическая операция (модификатор).

SE0 — выбор операций.

| PIN = | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

|

| 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 |

|

| MO | SE3 | SE2 | SE1 | SE0 | |||

Таблица операций АЛУ

| Выбор операции | Логические операции | Арифметические операции y5=МО=0 | ||||

| y4 SE3 | y3 SE2 | y2 SE1 | y1 SE0 | Без переноса С0=0 | С переносом С0=1 | |

| 0 | 0 | 0 | 0 | S = A | S = A | S = A + 1 |

| 0 | 0 | 0 | 1 | S = AVB | S = AVB | S = AVB + 1 |

| 0 | 0 | 1 | 0 | S = AɅB | S = AVB | S = AVB + 1 |

| 0 | 0 | 1 | 1 | S = 0 | S = -1 | S = 0 |

| 0 | 1 | 0 | 0 | S = AɅB | S = A + AɅB | S = A + AɅB + 1 |

| 0 | 1 | 0 | 1 | S = B | S = AVB + AVB | S = AVB + AVB + 1 |

| 0 | 1 | 1 | 0 | S = A⊕B | S = A - B - 1 | S = A - B |

| 0 | 1 | 1 | 1 | S = AɅB | S = AɅB - 1 | S = AɅB |

| 1 | 0 | 0 | 0 | S = AVB | S = A + AɅB | S = A + AɅB + 1 |

| 1 | 0 | 0 | 1 | S = A⊕B | S = A + B | S = A + B + 1 |

| 1 | 0 | 1 | 0 | S = B | S = AɅB + AɅB | S = AɅB + AɅB + 1 |

| 1 | 0 | 1 | 1 | S = AɅB | S = AɅB - 1 | S = AɅB |

| 1 | 1 | 0 | 0 | S = 1 | S = A + A* | S = A + A* + 1 |

| 1 | 1 | 0 | 1 | S = AVB | S = AVB + A | S = AVB + A + 1 |

| 1 | 1 | 1 | 0 | S = AVB | S = AVB + A | S = AVB + A + 1 |

| 1 | 1 | 1 | 1 | S = A | S = A - 1 | S = A |

В таблице отмечен вариант, который будет использоваться в этом курсовом проекте.

С помощью этого типового набора операций АЛУ строятся команды процессора с усеченной системой команд (RISC-архитектура).

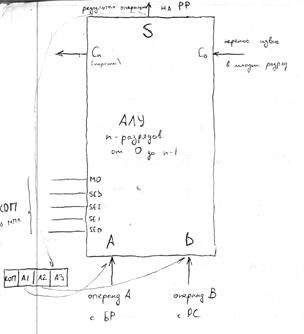

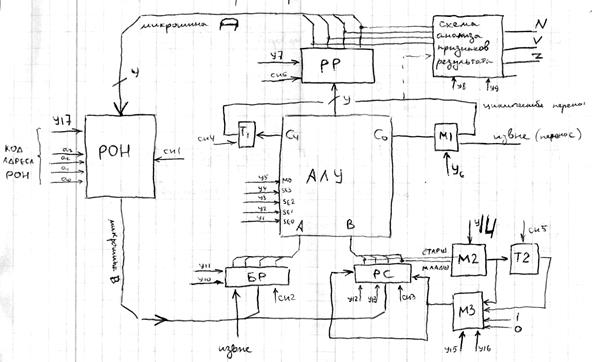

Общая схема регистрового АЛУ:

Управляющие сигналы уi составляют одну микрокоманду, существуют в течение одного такта и служат для установки узлов РАЛУ на выполнение соответствующих микроопераций.

У любого регистра есть следующие операции: запись, хранение, чтение. Для регистра сдвига добавляются еще две — сдвиг влево, сдвиг вправо.

Мультиплексоры — это устройства, которые переключают цепь с нескольких устройств на одно.

М1 — мультиплексор цепи переноса АЛУ.

Ко входу младшего разряда переноса АЛУ при у6=0 подключается внешний перенос (в случае построения многоразрядных сумматоров), при у6=1 подключается собственный перенос. Еще этот мультиплексор может вызвать прерывание V (переполнение).

М2 — мультиплексор цепи сдвига регистра сдвига РС.

Ко входу триггера сдвига Т2 при у14=1 подключается выход младшего разряда РС, при у14=0 подключается выход старшего разряда.

М3 — мультиплексор цепи сдвига.

Ко входам старшего и младшего разрядов РС подключается один из следующих сигналов:

| у15 | у16 | |

| 0 | 0 | Выход М2 |

| 0 | 1 | Выход Т1 |

| 1 | 0 | Логическая «1» |

| 1 | 1 | Логический «0» |

Первая комбинация соответствует организации циклического сдвига, когда при сдвиге вправо значение младшего разряда записывается в старший, а при сдвиге влево — значение младшего в старший. Вторая, третья и четвертая комбинации отличаются тем, что освобождающийся разряд записывается соответственно либо содержимое триггера Т2 (разряд, вытесненный при сдвиге в предыдущих тактах), либо логическая единица, либо логический ноль.

Остальные управляющие сигналы:

у1 — у5 определяют тип операции в АЛУ в соответствии с таблицей

у7 = 1 прием информации на РР с выхода АЛУ

у10 = 1 прием информации на БР

у11 = 0 в БР записывается информация с внешнего входа

у11 = 1 в БР записывается информация с микрошины В

| у12 | у13 |

| обеспечивают режим работы РС |

| 0 | 0 | приём информации с микрошины В | |

| 0 | 1 | правый сдвиг | |

| 1 | 0 | левый сдвиг | |

| 1 | 1 | хранение информации |

у17 = 1 запись информации в РОН

у17 = 0 хранение и чтение из указанного адреса РОН

у8 и у9 управляют формированием сигналов N (флаг знака), V (флаг переполнения), Z (флаг нулевого модуля)

Для корректной работы нам также потребуются синхроимпульсы, по которым будет происходить запись информации в триггеры регистров.

Этап 2. Техническое задание.

| |||

| |||

Нужно определить множества значений на входе и на входе, а также множество состояний, в которых может находиться наше устройство.

На входе мы получаем значения {MO, SE3, SE2, SE1, SE0}.

На выходе мы должны получить значение управляющих сигналов {уi}.

Для простоты будем полагать, что операнды находятся в РОНах, и результат запишем туда же.

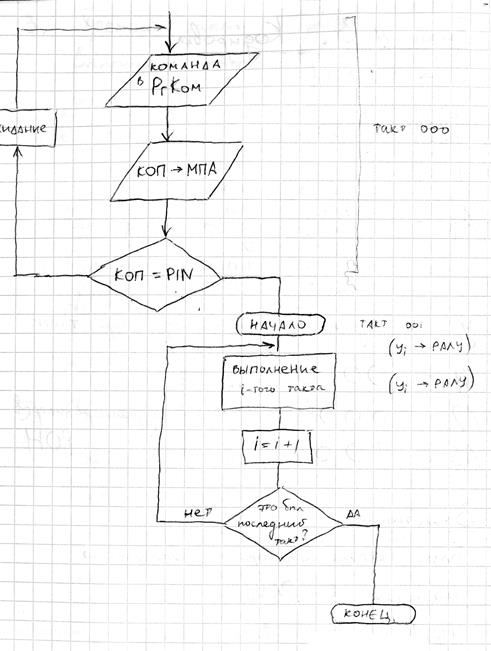

Множество состояний определим с помощью таблицы потактового выполнения операции.

Наша операция, определенная по PIN-коду (10001) — S=AVB.

A: A1

B: A2

S: A3

0. Ожидание.

1. Первый такт. Пересылка.

Пересылка операнда А из РОН А1 в БР

у17=0 (чтение), у10=1 (приём), у11=1 (с шины В)

2. Второй такт. Пересылка.

Адресуем А2, открываем его и записываем в РС.

Пересылка операнда В из РОН А2 в РС.

у17=0, у12=0, у13=0

3. Третий такт. Выполнение.

Выполнение операции в АЛУ, запись результата в РР.

КОП → АЛУ, у7=1 (приём на РР результата), формирование NZV-флагов → РССП

4. Четвертый такт. Пересылка.

Пересылка результата операции на АЛУ по адресу А3.

у17=0 (запись в РОН)

5. Пятый такт. Увеличение счетчика.

Формируется +1 в САК (счетчике адресов команд).

Сброс МПА в исходное состояние. Переход в состояние ожидания.

Всего у нас шесть состояний микропрограммного автомата.

Этап 3. Кодирование элементов.

{X} → {MO, SE3, SE2, SE1, SE0} → {10001}

{A} →

| Такт 0 | 000 |

| Такт 1 | 001 |

| Такт 2 | 010 |

| Такт 3 | 011 |

| Такт 4 | 100 |

| Такт 5 | 101 |

Закодируем адреса регистров РОН:

А1 = 0010 (№2), А2 = 0001 (№1), А3 = 1001 (№9).

Блок-схема алгоритма выполнения операции в РАЛУ:

|

Этап 4. Составление таблицы переходов и выходов.

| такт | КОП | сигналы управления | адрес регистра | такт | ||||||||||||||||||||

| Q2 | Q1 | Q0 | y1 | y2 | y3 | y4 | y5 | y6 | y7 | y8 | y9 | y10 | y11 | y12 | y13 | y14 | y15 | y16 | y17 | Q3 | Q2 | Q1 | Q0 | № |

| 0 | 0 | 0 | - | - | - | - | - | - | 0 | - | - | 0 | 1 | 1 | 1 | - | - | - | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | - | 0 | - | - | 1 | 1 | 1 | 1 | - | - | - | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | - | 0 | - | - | 0 | 1 | 0 | 0 | - | - | - | 0 | 0 | 0 | 0 | 1 | 2 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | - | 1 | - | - | 0 | 1 | 1 | 1 | - | - | - | 0 | 0 | 0 | 0 | 0 | 3 |

| 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | - | 0 | - | - | 0 | 1 | 1 | 1 | - | - | - | 1 | 1 | 0 | 0 | 1 | 4 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | - | 0 | - | - | 0 | 1 | 1 | 1 | - | - | - | 0 | 0 | 0 | 0 | 0 | 5 |

Все сигналы, управляющие режимом регистров, должны находиться в состоянии хранения на нулевом такте.

Полученная таблица является ТИ для функций у6 — у17.

Управление мультиплексорами в рассмотрение не берем, а константу у11 опустим (её легко можно заменить постоянной подачей ВУ).

Таким образом, наши функции — это у7, у10, у12, у13, у17.

Очевидно, что логические уравнения для этих функций получаются не слишком простыми. Поэтому мы реализуем МПА на перепрограммируемом постоянном запоминающем устройстве (ППЗУ/PROM).

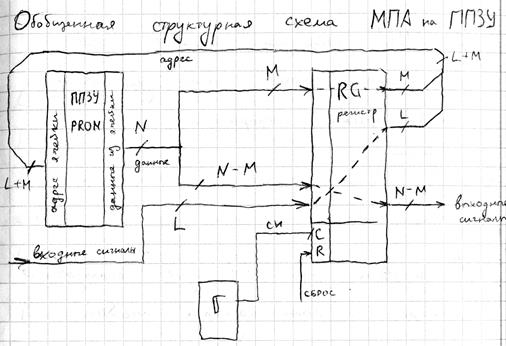

МПА состоит из ППЗУ (PROM) с L+M адресными битовыми входами, (N+L)-разрядного регистра и тактового генератора Г.

МПА состоит из ППЗУ (PROM) с L+M адресными битовыми входами, (N+L)-разрядного регистра и тактового генератора Г.

Часть входных разрядов ППЗУ (N—M) используется для формирования выходных сигналов, а остальные m разрядов участвуют совместно с L входными сигналами в формировании адреса ППЗУ в следующем такте тактового генератора.

В МПА необходимо применять только те регистры, которые имеют динамический способ приема информации. В противном случае (в случае использования регистра с потенциальным способом приема информации, при переходе регистра в режим пропускания информации на выход (при установке СИ=1) замкнется обратная связь по адресу и возникнет неконтролируемая автогенерация.

При этом tприёма информации < tзадержки ППЗУ + tзадержки регистров

Максимальная тактовая частота

Tmin = tзадержки ППЗУ + tзадержки регистров

Fmin = 1/Tmin

В нашем ППЗУ будет находиться его прошивка, а программа полностью связана с линейностью памяти. Можно прямо в микропрограмме явным образом указать, где находится следующая команда. Это позволяет отказаться от использования счетчика адресов команд.

Возможные режимы работы МПА:

- Последовательный перебор адресов ППЗУ.

(аналог счетчика САК в ЦП) - Останов в заданном адресе ППЗУ с произвольным количеством тактов ожидания изменения входного сигнала.

- Переход на другой адрес при изменении входного сигнала (одного или нескольких)

- Циклическое прохождение, т.е. перебор одних и тех же адресов ППЗУ.

- Отключение реакции на входные сигналы в течение какого-либо числа тактов.

Если состояний немного (до десяти), автомат можно задать графом и автоматными таблицами переходов и выходов (что мы и делали до этого). Если это не удается, строят ленты автомата — временные диаграммы. Они показывают фазовые отношения между входным и выходным сигналами. По ним выбирают временные сечения, которые рассматривают как вершины графа, то есть как состояния автомата.

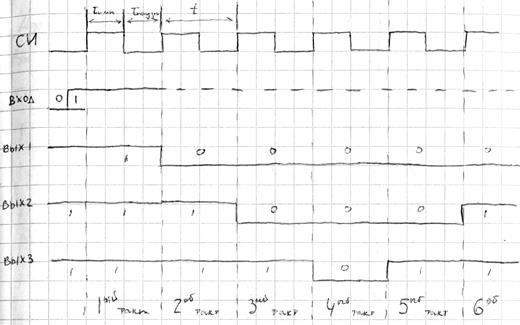

Мы будем проектировать МПА, работающий в соответствии со следующей временной диаграммой.

При подаче на вход ВУ, МПА должен вырабатывать три выходных сигнала, вложенных один в другой. Во время формирования выходной последовательности МПА не должен реагировать на входной сигнал, а после её окончания должен ожидать следующего ВУ на входе.

Временные сдвиги (такты) должны быть по 1мкс каждый.

Тактовая частота — 1 МГц при Q=T/tипм=2 (меандр).

Составим кодированную таблицу переходов и выходов:

| t | t+1 | ||||

| выход1 | выход2 | выход3 | выход1 | выход2 | выход3 |

| 1 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 |

Составим прошивку ППЗУ:

Необходимо реализовать следующие режимы работы:

- Последовательный перебор адресов при формировании отработки выходной последовательности.

- Останов с ожиданием изменения входного сигнала.

- Отключение реакции на входной сигнал путем дублирования последовательного перебора в зоне адресов, соответствующих изменению входного сигнала.

| Адрес ППЗУ | Данные ППЗУ | Режим работы | Ячейка | ||||||||

| Вход | Адрес | Выходы | Смещение | ||||||||

| 1 | 2 | 3 | |||||||||

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | Ожидание входного сигнала | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | Отработка входной последовательности | 8 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 9 | |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 10 | |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 11 | |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 12 | |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | Ожидание снятия входного сигнала | 13 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | Отработка входной последовательности | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 2 | |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 3 | |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 4 | |

| 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | Переход на ожидание входного сигнала | 5 |

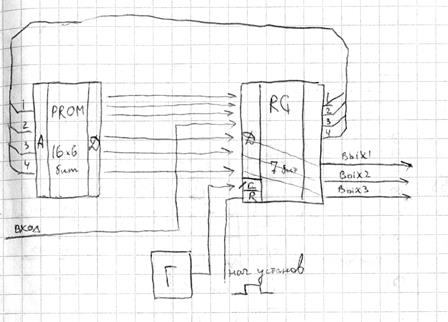

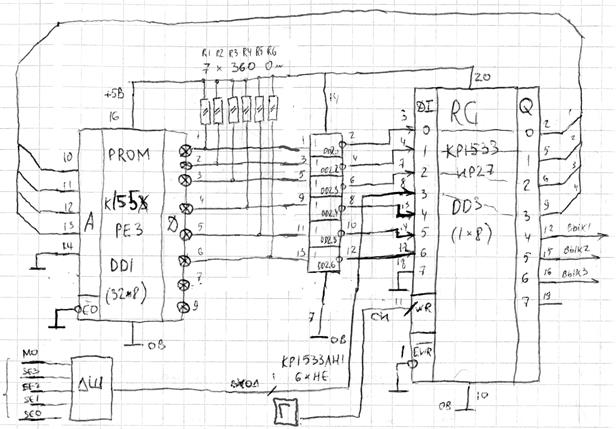

Функциональная схема.

Согласно временной диаграмме, выходная последовательность состоит из 6 тактов, включая единичные уровни. Поэтому требуется 3 отдельных входа ППЗУ, что дает 8 различных адресов. Кроме этого есть один входной сигнал. Следовательно, количество адресных разрядов ППЗУ — четыре, что дает 16 ячеек, а количество разрядов в каждой ячейке должно быть равно 6.

3 разряда — формирование выхода.

3 разряда — формирование следующего адреса.

Количество разрядов в регистре равно 6 + 1 входной сигнал — итого 7.

На схеме Г — тактовый генератор.

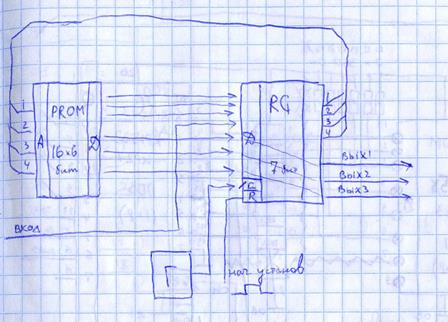

Принципиальная схема.

Замечание: крестом обозначены выходы с открытым (оторванным) коллектором. К ним должны быть присоединены резисторы R1 — R6.

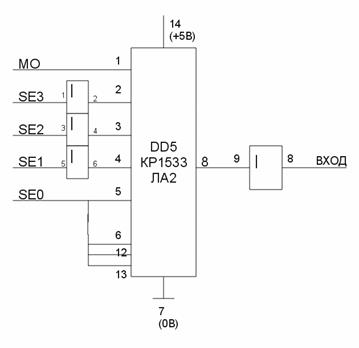

Схема дешифратора ДШ:

|

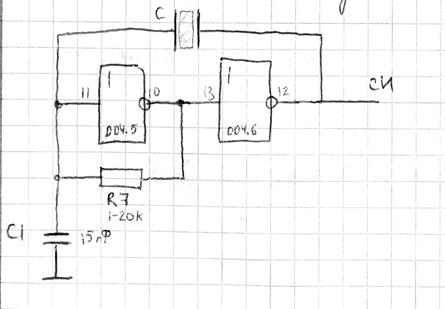

Схема генератора Г:

|

Теперь осталось только записать прошивку в ППЗУ. Так мы реализуем ТИ для данного автомата.

Для прошивки используем 12 ячеек памяти (6 основных + 6 дублированных на тот случай, если вход уберут раньше, чем закончить работать программа) с адресами вида 0хххх (нижний банк памяти) от 0 до 16.