До найважливіших параметрів ЗП належать інформаційна місткість і швидкодія.

Місткість ЗП (або об'єм пам'яті) визначається максимально можливим обсягом збереженої інформації, який задається кількістю або біт, байт, або слів з вказанням їх розрядності. Отже, у першому випадку місткість ЗП вимірюється в бітах або в байтах як добуток числа запам'ятовувачів n на розрядність m слів nm, а в другому випадку у розкритій формі – n´m. Наприклад, позначення ЗП у формі 64х8 біт означає, що ЗП місткістю 512 біт (або 64 байт) здатна зберігати 64 слова по 8 розрядів. Збільшення об'єму пам'яті розширює функціональні можливості цифрових пристроїв. Одночасно із збільшенням об'єму пам'яті зростає час звертання до ЗП, тобто підвищуються вимоги до швидкодії.

Швидкодія 3П характеризується періодом звертання (або часом циклу пам'яті) TЗВ і часом вибірки (або часом доступу до пам'яті ) tВ. Період звертання TЗВ - мінімально припустимий час між двома черговими звертаннями до ЗП. Цей параметр залежить від характеристики і властивостей ЗП відновлюватися після попереднього звертання до нього. Час вибірки tВ - інтервал часу між моментом подачі сигналу вибірки до появи інформації на виході ЗП. Різновидами цього параметру є час доступу при зчитуванні та час доступу при запису. З появою ВІС ЗП високої інтеграції час вибірки tВ наближається до пікосекундного діапазону.

Решта параметрів та характеристик інтегральних ЗП: споживана потужність віднесена до місткості ЗП, навантажувальна здатність, завадостійкість, логічні рівні та надійність визначаються так само, як і для інших типів мікросхем ЦТ.

Основою будь-якого ЗП є запам'ятовувач, що являє собою елементарну комірку пам'яті, яка здатна зберігати, а при звертанні до неї - записувати чи зчитувати 1 біт інформації, тобто один розряд двійкового слова. Таким запам'ятовувачем, як правило, є тригер. Стани 0 і 1 можна зберігати також і за допомогою конденсатора з ключем, роль яких найчастіше відіграють польові транзистори. Запам'ятовувачі на тригерах належать до статичних, а на конденсаторах - до динамічних. Такий поділ зумовлений тим, що термін "динамічний" на відміну від терміну "статичний" підтверджує часові зміни, що викликані неминучими струмами витікання конденсатора, який після запису все ж розряджається, а при зчитуванні зарядженого стану частина заряду "розтікається" по шині зчитування. Тому динамічну пам'ять час від часу необхідно регенерувати, тобто періодично підзаряджати. За динамічним принципом будуються ЗП великого об'єму.

Для зберігання невеликого масиву двійкових слів можуть використовуватися регістри і навіть дешифратори. Але вже при необхідності запам'ятовувати десятки слів об'ємом у тисячі біт без спеціально для цього зконструйованих і організованих ЗП обійтись неможливо. Тому 3П великих об'ємів будують об'єднанням окремих запам'ятовувачів, що нагадують бджолині соти.

Щоб суттєво скоротити число зовнішніх виводів таких ЗП, застосовують матрицевий принцип побудови. Матриця ЗП має всього дві шини - запису і зчитування, на перетинах яких знаходяться запам'ятовувачі. Оскільки звертання /запис або зчитування/ має здійснюватися тільки до одного запам'ятовувача,то для цього застосовують адресну вибірку, згідно з якою шукану комірку знаходять за номером стовпчика і рядка, тобто за адресою. Для зображення адрес застосовують комбінації m-розрядного двійкового коду. Отже, число запам'ятовувачів ЗП може складати n=2m.

Таким чином, за способом зберігання інформації ВІС ЗП класифікують:

· на статичні ЗП. запам'ятовувачі яких являють собою тригери, фізичний стан яких під час звертання не руйнується;

· на динамічні ЗП. які побудовані на конденсаторних запам'ятовувачах, що вимагають періодичної регенераціі за допомогою спеціальної схеми.

За організаційним принципом розробляють одно-(n´1) та багаторозрядні (n´m) BIС ЗП, де п, т. - відповідно число адрес і розрядів слів, які може зберігати ЗП.

За функціональною ознакою інтегральні ЗП розподіляють на два класи; оперативні та постійні.

Оперативні ЗП (ОЗП, RAM від англ. Random Accses Memory - пам'ять з довільною вибіркою) виконують операції звертання довільної двійкової інформації майже за однаковий час. ОЗП призначені для тимчасового зберігання біжучої інформації і швидкого звертання до запам'ятовувачів. Розрізняють енергозалежні ОЗП, які зберігають інформацію лише при наявності напруги живлення, і енергонезалежні. ОЗП умовно поділяють на три основних типи: середньої місткості помірної швидкодії, високої швидкодії - надоперативні ОЗП і ОЗП великої місткості.

Постійні ЗП (ПЗП, ROM- від англ. Read Only Memory – пам'ять тільки для читання) призначені для тривалого, зберігання і швидкого зчитування постійно записаної раніше інформації, зміст якої під час експлуатації ЗП не змінюється, а при відсутності живлення не руйнується. Отже, у ПЗП передбачені лише два режими роботи - зберігання і зчитування. На відміну від ПЗП перепрограмовані ПЗП (ППЗП) допускають відновлення занесеної інформації, тобто у них передбачається режим запису. Цей процес реалізують за допомогою спеціально призначених для цього пристроїв (програматорів).

За способом звертання до запам'ятовувачів ВІС ЗП розрізняють:

· на адресні ЗП з довільним звертанням і ЗП з послідовним звертанням, тобто з вибіркою при. збільшенні або при зменшенні адресного коду;

· на асоціативні (безадресні) ЗП. пошук інформації у яких здійснюється незалежно від координат запам'ятовувачів, тобто не за адресою, а за певними ознаками самої інформації, що міститься у запам'ятовувачі ЗП.

За технологічним виконанням ВІС ЗП поділяють на біполярні, що використовують схемотехніку ТТЛ і ЕЗЛ, ЗП на основі МОН-структур /р‑MОН, n-МОН, КМОН/ та інжекційну І2Л-технологію.

5.2 Оперативні запам'ятовуючі пристрої

Для побудови ОЗП або ЗП з довільною вибіркою інформації використовується практично вся відома на сьогодні схемотехніка - ТТЛ/Ш/ЕЗЛ, /К/МОН, І2Л тощо. ВІС ОЗП виконуються як статичні, так і динамічні.

5.2.1 Статичні запам'ятовувачі ВІС ОЗП

Це двостанові комірки пам'яті - тригери, які крім зберігання одиниці біт інформації (1 або 0), дозволяють здійснювати операцію звертання WR/RD. Вони є найбільш поширеними у практиці цифрової та мікропроцесорної техніки і застосовуються як регістри процесорів надоперативної та буферної пам'яті.

За технологічним виконанням статичні запам'ятовувачі розрізняють на біполярні та польові. Біполярні запам'ятовувачі, хоч і мають серед статичних ОЗП найвищу швидкодію (tВ=5...50нс), однак порівняно з польовими (на ПТ) мають значно меншу інформаційну місткість і досить значну потужність споживання. Це пояснюється тим, що польові запам'ятовувачі займають на кристалі у кілька разів меншу площу, ніж біполярні, та й споживають менший струм.

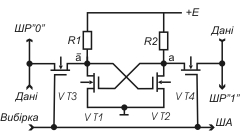

На рис. 6.1 зображено схему статичного польового запам'ятовувача на базі n-МОН-структури. Транзистори VТ1 і VТ2 утворюють тригер, а транзистори VТЗ і VТ4 - двонапрямлені ключі вводу/виводу даних, тобто звертання WR/RD. Резистори навантаження R1 і R2 мають високі номінали опорів для забезпечення низького споживання у режимі зберігання.

Схема польового запам'ятовувача має три інформаційні виводи, від логічних станів (0 або 1) на яких залежить той чи інший режим роботи. Зокрема, це два виводи (станів  і

і  тригера) шин розрядів (ШР) "1" і ШР "0" і вивід вибірки схеми - шини адреси (ША).

тригера) шин розрядів (ШР) "1" і ШР "0" і вивід вибірки схеми - шини адреси (ША).

Рис. 5.1 Статична однобітова комірка пам’яті на польових транзисторах

У режимі запам'ятовування транзистори VТ3 і VТ4 закриті, а у режимі звертання WR/RD - відкриті. Режим запам'ятовування визначає низький потенціал на АШ, а звертання - високий. В останньому випадку, коли транзистори VТЗ і VТ4 відкриті і стають провідними в обох напрямках, можна виконувати як запис, так і зчитування інформації.

У режимі запису на ШР "1" і ШР "0" встановлюються високий або низький рівні сигналів, які відкривають транзистор VТ1 або VТ2, і тригер переходить в стан лог. 0 або лог. 1. При зчитуванні інформації із запам'ятовувача на ШР "1" і ШР "0" подається високий потенціал джерела живлення. У результаті цього розряджається паразитна ємність шини (ШР "1" або ШР "0"), яка зв'язана з відкритим транзистором (VT1 або VТ2) тригера. У відкритому транзисторі потенціал на виході близький до нуля (наприклад, якщо VТ1 відкритий, то  =0, а Q=1, бо VТ2 – закритий). Отже, при відповідній різниці потенціалів на розрядних шинах (ШР "1"=0, а ШР "0"=1 чи навпаки) дана інформація із запам'ятовувача буде зчитуватися на вихідні буферні підсилювачі шин.

=0, а Q=1, бо VТ2 – закритий). Отже, при відповідній різниці потенціалів на розрядних шинах (ШР "1"=0, а ШР "0"=1 чи навпаки) дана інформація із запам'ятовувача буде зчитуватися на вихідні буферні підсилювачі шин.

Порівняно з іншими статичні запам'ятовувачі на КМОН-транзисторах споживають найменше потужності. Наприклад, потужність розсіювання у КМОН ВІС ОЗП КР537РУ2А, місткість якого 4К, складає всього 0,5мВт у режимі зберігання і 20мВт у режимі перемикання (звертання). Статичні ВІС ОЗП середньої швидкодії, що виконані на n-МОН-, КМОН- та І2Л-технологіях, мають період циклу звертання до запам'ятовувачів від сотень наносекунд до одиниць мікроcекунд. Перспективними ВІС ОЗП є, однак, ЗП на базі арсеніду галію. Потужність розсіювання у режимі звертання у таких ВІС складає не більше 10мкВт/біт, а час вибірки не перевищує 10нс.

У структурі ВІС ОЗП статичні запам'ятовувачі компонуються у прямокутну матрицю розміром п´m ( де n - число m-розрядних слів), яку називають накопичувачем ЗП. Кожний рядок накопичувача – це адресна шина вибірки, а стовпець – дві розрядні шини звертання ШР "1" і ШР "0" запам'ятовувача.

5.2.2 Динамічні запам'ятовувачі ВІС ОЗП

Їх також виконують на біполярних та польових транзисторах. Відмінність побудови схем динамічних запам'ятовувачів полягає у способі запам'ятовування двійкової інформаціі, який реалізується зарядом або розрядом паразитної ємності. Схему динамічного запам'ятовувача виконують на базі одного або трьох транзисторів. На відміну від статичного запам'ятовувача динамічний значно простіший і економічніший, бо вимагає вдвічі меншого числа транзисторів, і, отже, на однакових розмірах кристалу дозволяє вдвоє збільшити інформаційну місткість. Тому динамічні ОЗП дають змогу будувати ВІС надвеликих місткостей. Перевага динамічних запам'ятовувачів ще в тому, що їм не потрібне джерело живлення.

Оскільки значення паразитної ємності, як правило, не перевищує 0,1пФ, стала часу розряду накопичувального конденсатора є досить значною - не менше 1мс. Тому, щоб розрізнити одиницю інформації /0 або 1/, яка зберігається у вигляді заряду, необхідно її відновлювати, тобто регенерувати, причому з періодом регенерації не менше від 1мс. Це ускладнює схему запам'ятовувача і організацію структури ВІС ОЗП у цілому.

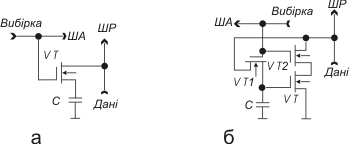

На рис. 5.2.а,б показано схеми динамічних одно- та тритранзисторного запам'ятовувачів ОЗП, які найбільш поширені у ВІС ОЗП великої місткості /> 16К/. В обох схемах запам'ятовувачів зберігання двійкової інформації здійснюється на конденсаторі C, а транзистор VТ відіграє роль перемикача, що передає заряд конденсатора C у розрядну шину при зчитуванні або розряджає його при записі інформації.

Рис. 5.2 Схеми динамічних запам’ятовувачів

Спільним для наведених тут схем на базі n-МОН-транзисторів динамічних запам'ятовувачів є також те, що для отримання можливості зчитувати інформацію конденсатор С попередньо заряджають, імпульсами високого рівня, які подають на ШР при активізації вибірки, тобто при подачі високого рівня на ША.

Отже, записування інформації в однотранзисторному запам'ятовувачі відбувається подачею високого потенціалу на ШР на відкритий транзистор, а зчитування - струмом розряду конденсатора в ШР з руйнуванням інформації. У тритранзиcторного запам'ятовувача накопичувальний конденсатор ізольований від ШР, і тому зчитування інформації відбувається без її руйнування. Проте через струми витікання у конденсаторі потрібна періодична регенерація інформації. Цей процес досягається подачею високого потенціалу на ША і спеціальною схемою регенерації, яку під'єднують до ШР.

Регенерація динамічного запам'ятовувача ОЗП здійснюється за кожним звертанням до нього. Схема регенератора-підсилювача автоматично виконує цей процес при звертанні до cтовпця накопичувача з інтервалами близько сотні мікросекунд. Динамічні ОЗП побудовані так, що сам процес звертання до стовпця забезпечує регенерацію інформації в усіх його запам'ятовувачах.

5.2.3 Принцип побудови і структура ВІС ОЗП

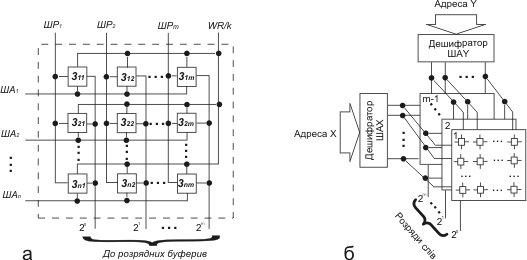

Вони визначаються основним вузлом ЗП – n´m-матрицею запам'ятовувачів, яку називають накопичувачем інформації. Відомо кілька способів організації запам'ятовувачів у накопичувачі. Залежно від способу звертання WR/RD до запам'ятовувачів розрізняють два найбільш поширених типи організації накопичувачів:

· з однокоординатною (або послівною) вибіркою;

· з двокоординатною вибіркою.

При однокоординатній вибірці реалізується пошук групи запам'ятовувачів за одною адресою, тобто однією шиною ША вибирається тільки одне з усіх n m-розрядне слово. Як показано на рис. 5.3.а, такий накопичувач ОЗП має адресні шини ША1, ША2,..., ШАn , що з'єднані з кожним запам'ятовувачем Зij одноіменного і-го слова, і розрядні шини ШР1, ШР2, ...,ШРm , які з'єднані з одноіменним j-m розрядом усіх її. слів. Крім того, існує ще спільна для всіх n ´m. запам'ятовувачів (3nm) шина звертання WR/RD, сигнал на якій визначає режим звертання - запису або зчитування. Отже, при появі на одній з адресних шин ШАi сигналу вибірки і -го слова, наприклад при активному високому рівні. Інформацію з кожного запам'ятовувача Зi1, Зi2,…, Зim i-го рядка (тобто і-го слова) можна зчитувати шляхом активізації розрядних шин ШР1, ШР2, ..., ШРm.

Для запису слова, наприклад, у комірку запам'ятовувачів З21, З22,..., З2m, слід активізувати другий рядок накопичувача, тобто адресну шину ША2, а на всі розрядні шини ШР1, ШР2, ..., ШРm - прикладати значення розрядів (0 або 1) записуваного слова. При цьому на шину WR/RD треба подати сигнал дозволу на запис інформації. Після зчитування записаної інформації на вході розрядних буферів (вихідних підсилювачів ОЗП) з'являються рівні напруг, що відповідають значенням розрядів (0 або 1) зчитаного слова.

Розглянутий тип організації накопичувача інформації має лише одну координату звертання до запам'ятовувачів, а саме - номер рядка накопичувача. Тому для однокоординатного накопичувача досить одного дешифратора адреси. Накопичувач з однокоординатною вибіркою називають ще двовимірним - типу 2D , бо запам'ятовувачі у ньому розташовані на площині.

Рис. 5.3 Структурні схеми накопичувачів інформації

У структурній схемі накопичувача з двокоординатною вибіркою (рис. 5.3,б) потрібну комірку запам'ятовувача шукають за допомогою двох адресних шин, - горизонтальних (по рядках) ШАХ і вертикальних (по стовпцях) ШАY, і розрядної шини ШР. Накопичувач за такою структурою, має тривимірну будову і складається з m накопичувачів розрядів, кожний з яких містить n запам'ятовувачів. Отже, кожний накопичувач відповідає тільки за один одноіменний розряд всіх n слів, а кожне слово записується, зберігається і зчитується в усіх т. накопичувачах за ідентичною двокоординатною адресою Хi, Yi.

Для запису слова у запам'ятовувач за адресою Хi, Yi. на входи адресних дешифраторів ШАХ і ШАY подаються відповідні коди Хi, Yi, а двійкове значення слова - на спільні розрядні шини ШР1, ШР2, ..., ШРm. Аналогічно здійснюється зчитування записаного слова.

5.3 Принцип побудови і структура ПЗП

Порівняно з ОЗП ВІС пап мають простішу організацію пам’яті та схему керування процесом зчитування інформації. Загальною ознакою всіх ПЗП є також наявність двокоординатної матриці-накопичувача, що являє собою однорідне за технологією “поле” запам’ятовувачів.

ВІС ПЗП дуже нагадують ПЛМ, бо також складаються з матриць; тільки у ПЗП програмують не обидві матриці (кон’юнкцій та диз'юнкцій), а лише матрицю диз’юнкцій. Матриця кон’юнкцій у ній відіграє роль “жорсткого” повного дешифратора всіх 2 n вихідних від n вхідних комбінацій. Тому ПЗП має більше ніж у ПЛМ число входів – рівно стільки, скільки потрібно для забезпечення повної таблиці істинності всіх n адрес. Незважаючи на відмінність у сфері застосування ПЛМ за спільністю ознак часто відносять до класу ЗП як особливий вид ПЗП.

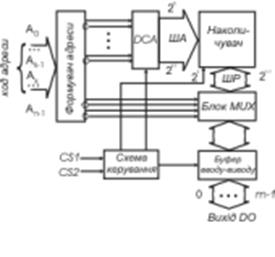

На рис. 5.4 показана узагальнена структурна схема ВІС ПЗП, основою якої є накопичувач інформації, що з’днаний через ША з дешифратором адрес (DСА), а через ШР - з блоком мультиплексорів (МUX) Паралельний код адреси А подається на формувач адрес, парафазні сигнали якого надходять на DСА і блок МUX, які збуджують одну з горизонтальних (адресних) шин ША. Зчитування записаної у запам’ятовувачах інформації відбувається по всіх вертикальних (розрядних) шин ШР через блок мультиплексорів і буфер вводу/виводу. Схема керування синхронізує роботу DСА і блок МUX, а також служить для забезпечення можливості нарощування об’єму пам’яті об'єднанням виходів (як монтажне АБО для схем з відкритим колектором) кількох ВІС ПЗП або для забезпечення їх роботи на спільну шину (для випадку тристанових виходів).

Рис. 5.4 Узагальнена структурна схема ВІС ПЗП

У ВІС РПЗП схема керування, крім того, керує режимами запису, зчитування та стирання інформації. На відміну від ОЗП при зчитуванні накопичувача ПЗП задається вміст цілого рядка запам’ятовувачів, причому такий рядок може містити навіть кілька слів. З вибраного дешифратором рядка виділяється і передається на вихід потрібне слово за допомогою мультиплексорів.

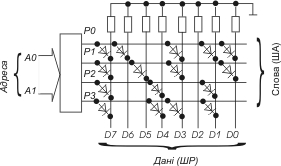

Для реалізації простого МПЗП досить використати дешифратор і потрібну для цього певну кількість діодів для побудови матриці-накопичувача. Такий МПЗП зображений на рис. 5.5. Він має місткість 25 = 32 біт, які розбиті на 22 = 4 слова по 23 = 8 розрядів у кожному. Отже, це ПЗП здатне запам’ятовувати чотири однобайтних слова (4х8=32біт).

Рис. 5.5 Діодний накопичувач інформації

У координатному полі накопичувача діоди, що відіграють роль запам’ятовувачів, розміщуються у тих “точках”, де повинні зберігатися біти, що мають значення лот. 1. Таким чином, для вибору потрібного слова треба за допомогою дешифратора 2-4 задати адресу {А1А0}, тобто активізувати один з виходів дешифратора Рі, що рівнозначно появі одиниці на обраній ША. Тоді на тих ШР, на перетинах яких з обраною ША присутній діод, формується одиниця, а на решті ШР - нуль.

Діодні накопичувачі, однак, не знайшли широкого застосування для побудови ВІС МПЗП через їх низьку швидкодію. Найбільшу швидкодії забезпечують біполярні накопичувачі, час звертання у яких < 20 нс. Хоч МОН-накопичувачі мають нижчу швидкодію (час звертання - близько 200...600 нс), однак потужність розсіювання їх значно нижча. Тому у ВІС МПЗП можна зустріти накопичувачі як біполярні, так і польові. Транзистори, що виконують роль запам’ятовувачів, у цих ВІС під’єднують до рядків і стовпців накопичувача так, як це показано на рис. 5.5. Так само, як і у діодного накопичувача, наявність або. відсутність транзистора у “точці” перетину ортогональних ліній також відповідає стану 1 або 0 запам’ятовувача.

Структура ВІС ППЗП аналогічна структурі ВІС МПЗП.. Подібно до ППЛМ запам’ятовувачі ППЗП найчастіше виготовляються разом з перемичками, які у процесі програмування при вибірці відповідного запам’ятовувача перепалюються електричним струмом достатньої напруги (до 10...12 В). Матеріали для перемичок - титано- вольфрамові, ніхромові та інші сплави. Інший тип запам’ятовувача передбачає закорочування зворотно ввімкнених діодів.

Рис. 5.6 Типове позначення ПЗП

Для програмування ППЗП необхідно насамперед скласти карту програмування, яка по суті є таблицею істинності, де кожній комбінації повного набору n адрес А0... А(n-1) відповідає код даних D0..D(n-1), який потрібно “зашити”. Режими програмування у різних мікросхем ППЗП різні, бо визначаються вони не лише технологією виготовлення даної ВІС, але й типом мікросхеми ППЗП (з відкритим колектором чи тристановим виходом тощо) та матеріалом самої перемички. Для перепалювання останніх використовуються спеціально призначений для цього пристрій -програматор, який має забезпечувати потрібний режим програмування ППЗП (тривалість імпульсу, його амплітуду і струм перепалювання) з допомогою одного імпульсу або пачки імпульсів.

Можливість програмувати робить ППЗП і особливо РПЗП універсальними пристроями ЦТ. У РПЗП можна багаторазово стирати записану інформацію і записувати нову. Тому для виявлення і виправлення помилок РПЗП на відміну від ППЗП є більш ефективними. У накопичувачах РПЗП використовуються спеціальні типи транзисторних структур, що побудовані, зокрема, на основі МОН-транзисторів з плаваючим (ізольованим) заслоном, які змінюють під час програмування свої характеристики. Ці зміни є ознакою стану збережуваної у ПЗП інформації.

Програмування накопичувачів РПЗП з ультрафіолетовим стиранням виконуються у два етапи - спочатку під дією інтенсивного ультрафіолетового випромінювання всі транзистори закриваються, що відповідав запису в усіх запам’ятовувачах лог. 1 (попереднє стирання), а потім за допомогою ША і ШР вибираються ті транзистори запам’ятовувачів, в які потрібно занести лот. 0 (запис інформації). Для цього на адресний вхід РПЗП подається код адреси слова, а на спеціальний вхід(СS-імпульс достатньої для перепалювання перемички напруги і потужності. При записі інформації у РПЗП часто застосовується програматор, керований мікропроцесором. На рис.5.6 показані умовніе графічне позначення ПЗП. Відмінності для різних типів ПЗП полягають в умовних скороченнях: для МПЗП це "ROM" (див. рис.5.6), для ППЗП – "PROM" для РПЗП– "RPROM".

Рис. 5.7 Способи збільшення розрядності даних ПЗП (а) та адрес (б)

Розширити функціональні можливості ПЗП різних типів можна за рахунок каскадування, тобто збільшення, їх інформаційної місткості. Процедуру нарощення ПЗП можна здійснити як для збільшення розрядності m слів, так і для збільшення числа n слів. Це рівнозначно збільшенню певного числа відповідно виходів або входів, яких не вистачає у даному ПЗП для реалізації поставленого завдання. Зрозуміло, що для цієї процедури потрібно мати необхідну кількість однотипних мікросхем ПЗП, а також виконати відповідну зовнішню комутацію виводів даного ПЗП з виводами інших ПЗП. Збільшити розрядності слів (число виходів) ПЗП досить просто - потрібну кількість мікросхем ПЗП вмикають паралельно по одноіменних входах так, як це показано на рад. 5.7.а. При цьому число виходів даних ПЗП від тих самих аргументів (адрес) стане більшим, що рівнозначно збільшенню розрядності. Для збільшення числа збережуваних слів даних застосовують вхід СS (вибір мікросхеми) (рис. 6.12,6). При Аn=0 адресується верхній модуль ПЗП, а при Аn=1 –нижній. Виходи обох модулів зв'язуються за схемою монтажного АБО.

5.4 Електрично перепрограмовувані ПЗП

В останній час особливого поширення набули електрично-перепрограмовувані мікросхеми EEPROM, які є подальшим розвитком вищеописаних ПЗП. Вони дозволяють здійснювати власний перезапис не тільки за допомогою програматорів, але й внутрішньосистемно – безпосередньо на платі цифрового пристрою. При цьому існують ІС паралельного типу, які функціонально нічим не відрізняються від розглянутих вище ПЗП і способи роботи з ними аналогічні до вищевикладених (за винятком програмування) та послідовного, які мають незначну кількість виводів (як правило 8) і обмін даними з ними відбувається за допомогою одного з послідовних протоколів (найчастіше MicroWire, I2C або SPI). Приклад ІС послідовного типу 2404. Такі ІС мають від 103 до 105 гарантованих циклів перезапису, що є набагато кращим показником у порівнянні з ПЗП, які стираються за допомогою ультрафіолетового випромінювання (до 100 разів). Послідовні ПЗП найчастіше використовуються для запам’ятовування допоміжної інформації в приладах перед переходом у вимкнений стан (різноманітні коди доступу, позиції регуляторів управління, тощо). Паралельні ПЗП використовуються для запису програм та значних масивів даних в мікропроцесорних пристроях. Оскільки алгоритми програмування таких ІС є доволі громіздкими вони будуть розглядатись в подальшому.

[*] Компаратор - з англ. compare-порівнювати (схемне позначення функції - СМР).

* Позначення - АLU від англ. Arithmetic and Logic Unit (арифметично-логічний пристрій).

[2] Тpигер - від англ. trigger - спусковий гачок; інша назва flip-flop.

* При оформленні технічної документації, курсових та дипломних робіт, зображення електричних елементів (ЛЕ, тригерів, транзтсторів) слід брати з відповідного стандарту. Не можна користуватись іншою літературою, оскільки там ці зображення можуть бути відтворені без дотримання всіх розмірів

* Від англ. Master-Slave –„пан-раб”